静态时序分析是什么(静态时序分析三种方法)

导语:看完彻底理解:静态时序分析

估计面试的时候都会让大家解释一下建立时间和保持时间,几乎所有人都能背出来。建立时间(setup time):时钟的有效沿到来之前数据必须提前稳定的时间。保持时间(hold time):时钟有效沿到来之后数据必须继续保持稳定的时间。

我们知道,整个ASIC设计流程主要两个目的:功能和性能。 除了要保证设计的功能,另外一个就是要保证性能。性能通俗的讲,主要是看电路跑得多快,也就是时钟频率有多高。保证性能的方法就是通过静态时序分析保证电路能够跑到要求的频率。而静态时序分析(Static Timing Analyze),其本质是检查电路中所有寄存器是否满足工艺库规定的固有建立时间和保持时间。可咋一看,寄存器的建立保持时间跟时钟周期是没有关系的。因此,带着这些困惑,我们一起来了解一下静态时序分析的真正原理。

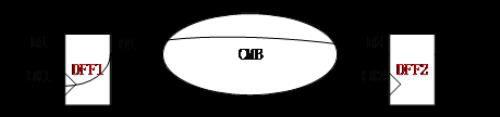

首先,所有电路都可以抽象成上图的形式,这是因为RTL(Register Transition Level)代码描述的是寄存器的传输行为,信号从DFF1通过组合逻辑CMB的行为,传输到DFF2。另外,静态时序分析都是假设所有信号每个周期都可能变化,也就是单周期检查。这样,D1从时钟沿开始,DFF1出来,通过组合逻辑CMB,下一个时钟沿,D2要能正确寄存在DFF2中,就需要满足建立和保持时间的要求。 因此, D1从时钟CK的上升沿开始,通过DFF1的CK->Q的延时Tck,组合逻辑的延时Tcmb,在第二个CK上升沿分析DFF2的建立和保持时间。

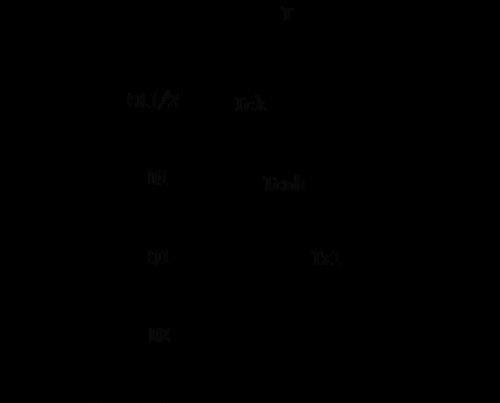

建立时间:Tx1 = T – Tck -Tcmb > Tsetupà Tck + Tcmb + Tsetup < T

如果考虑时钟的Skew,也就是CK1和CK2的时钟沿不是同时到达,对于悲观的影响,也就是CK2比CK1要提前到来Tskew时间,则

Tck + Tcmb + Tsetup + Tskew < TàTcmb < T – Tck – Tsetup – Tskew

因此,建立时间与时钟周期扯上关系了,也就是约束了组合逻辑的延时不能太大。

当然,对于乐观的Tskew,也就是CK2比CK1要晚到,这是有利于建立时间的,通过这个原理,可以在做时钟树时,特意的加大这个Tskew来修复建立时间违规,这就是后端常用的Useful skew技术。

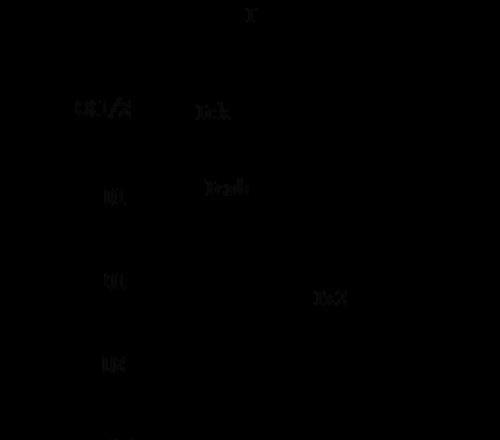

保持时间:Tx2 = Tck + Tcmb > Thold

如果考虑时钟Skew悲观的影响,也就是CK2比CK1要晚到来Tskew时间,

Tck + Tcmb > Thold + Tskew àTcmb > Thold+Tskew – Tck

因此,保持时间与时钟周期是没有关系的,它约束了组合逻辑的延时不能太小。

综上所述,静态时序分析,就是来约束电路中所有路径的以下关系,通俗的讲,就是组合逻辑的延时不能太大,也不能太小。

Thold + Tskew – Tck<Tcmb<T – Tck – Tsetup – Tskew

作者:Wayne Cao

注:©本文为“E课网”原创,版权归“E课网”所有欢迎分享。

免责声明:本站部份内容由优秀作者和原创用户编辑投稿,本站仅提供存储服务,不拥有所有权,不承担法律责任。若涉嫌侵权/违法的,请反馈,一经查实立刻删除内容。本文内容由快快网络小信创作整理编辑!