中断硬件机制怎么实现(硬件中断方式)

导语:中断的硬件实现机制讨论

当CPU用查询的方式与外设交换信息时,CPU就要浪费很多时间去等待外设。这样就引出一个快速的CPU与慢速的外设之间数据传送的矛盾,这也是计算机在发展过程中遇到的严重问题之一。为解决这个问题,一方面要提高外设的工作速度,另一方面发展了中断概念。中断系统是计算机的重要指标之一。

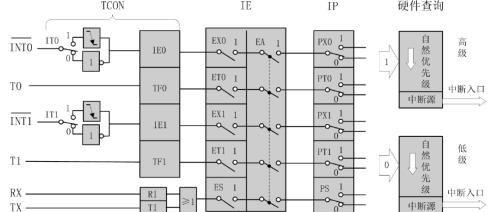

图一

图一是单片机的硬件中断控制系统。单片机51共有五个中断源。其中每个中断都由3个开关控制,一个是中断自身的控制开关,一个是总控开关,一个是优先级控制开关,所以,每一个中断要能够被执行,必须三个开关同时闭合。

图二

图三

上面说的三个开关同时闭合,就是图二、图三中的寄存器的相应位要置1。

上面说的单片机的中断控制机制很好理解,但图一其实只是一个示意图,比如中断优先级的控制直接以一个开关表示,那么,中断优先级真正的控制电路又是怎样的呢?

图四

图四是一个优先级排队器。很明显,当INTR1=1时,也就是INTR1存在中断请求时,此时

将为0,经过两次非门运算,将导致

均为0,也就是使得后面的中断都无效,只有当INTR1=0时,INTR2才会打开,从而实现了中断优先级排队。

除了上面的中断优先级排队之外,我们知道,中断还分为可屏蔽和不可屏蔽:

图五

从图五很容易看到屏蔽的原理。

接着给出一个I/O中断的全过程图。

图六

总之,当多个外部中断源共享中断资源,必须解决相应的一些问题,例如CPU芯片上只有一个INTR输入端,多个中断源如何与INTR连接、中断矢量如何区别、各中断源的优先级如何判定等。可编程中断控制器就是为此目的而设计的,它可以接收多个外部中断源的中断请求,并进行优先级判断,选中当前优先级最高的中断请求,并将此请求送到CPU的INTR端。当CPU响应中断并进入中断服务程序的处理过程后,中断控制器仍负责对外部中断请求的管理。例如当某个外部中断请求的优先级高于当前正在处理的中断的优先级时,中断控制器会让它通过送到CPU的INTR端,从而实现中断嵌套。反之,对其他级别较低的中断则予以禁止。

图七

图七中的有些步骤是由硬件完成的,比如第(1)(2)步,以及第五步入口地址的处理,也是由硬件自动向CS:IP寄存器输入地址实现的;而保护现场和恢复现场则是由push和pop指令实现的,第(7)步则又是由硬件实现的。

本文内容由小曲整理编辑!