d型触发器波形图(d型触发器的特征方程式)

导语:[电路小知识篇]D型触发器电路

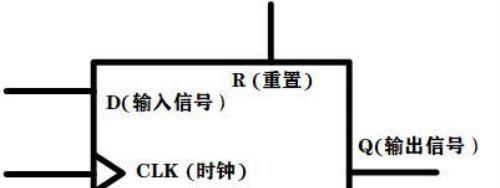

在基础电路设计中, D-触发器被广泛的用于短暂(一个或者几个时钟周期内)储存/传输信号,也可以长期储存信号(但是能耗以及电路面积占用较高)。D-触发器的示意图如下:

常见的D-触发器

常见的正向D-触发器工作原理较简单:当时钟信号从0变为1的时候,输出信号Q变为输入信号D的值。 重置信号R在正常工作时需要为1,如果重置信号R为0则输出信号Q为0。

典型的应用例如串行移位寄存器以及各种需要时钟周期的控制电路中。 下图即为一个典型的D触发器的应用(扫描链):

常见的扫描链(Scan Chain)应用

该电路的功能在于:假设我们有一个需要测试的芯片,里面有许多(例如,32个)可控输入信号(比如单片机的各种调试接口)。那么在我们设计这些芯片上的输入端时,将所有信号接到片外是一个非常不经济的行为。 这主要是因为芯片上的连接制作成本很低(几乎可以忽略不计),但是芯片内外的连接非常昂贵,需要各式各样的放大器以及保护电路,另外这些片外连接需要的芯片面积也不容小视。 因此,扫描链可以让我们轻松的实现只用3个片外信号(重置,输入以及时钟总线)来做到(理论上)任意多的芯片内可控输入。当然,输入这些信号和这些信号的数量成正比(也即每一个时钟周期只能输入一个信号)。

举个例子,如果我们的需要的内部信号为(32比特): 0011 1100 0011 1100 0011 1100 0011 1100 (最左侧为输出信号31, 最右侧为输出信号0),那么输入的方式即为:将输入设为0, 并且使时钟上下跳动2次; 然后输入设定为1,使时钟上下跳动4次 ... 以此类推。

那么在以上的应用中,有细心的读者可能会疑惑:为什么在一个时钟上升沿(也即在时钟由0变为1的同时), 原来的输入只会到并行输出0,并行输出0只会到并行输出1, 而不会继续向下传递呢?

这就要从D-触发器的原理说起了。简单地说, D-触发器“由时钟沿触发”的原理可以看成以下两个电路的结合:

D-触发器分解原理

前一部分电路可以理解成:当门信号为0时,允许输入信号D通过。后一部分电路和前一部分类似- 当门信号为1时,允许输入信号D通过。这样,如果我们将门信号连接到一起(也即时钟信号),该电路就变为了D-触发器。

那么, 这两组电路可以看成是以下示意图:

D-触发器示意图

我们把D-触发器想象成是两扇门,信号是一个可以在打开的门之间走动的小人,那么在时钟信号为低的时候,信号D1的小人可以通过第一扇门,但是无法通过第二扇门。同理,当时钟信号为高的时候, 信号D1可以通过第二扇门,但是注意, 此时新来的信号(信号D2)无法通过第一扇门了。因此,在每次时钟上升的时候, 只有前一次的信号可以通过D-触发器,而后一次来的信号是无法通过的。这种特性也使得D-触发器非常适合作为可控信号传递模块。

本文内容由小鸣整理编辑!