tft基板工艺(tft基板包括哪些结构)

导语:AMOLED TFT基板的制作方法(2)

AMOLED TFT基板的制作方法

技术领域

[0001]涉及显示技术领域,尤其涉及一种AMOLED基板的制作方法。

背景技术

[0002]在显示技术领域,液晶显示器(Liquid Crystal Display,LCD)与有机发光二极管显示器(Organic Light Emitting Diode,OLED)等平板显示技术已经逐步取代CRT显示器。其中,OLED具有自发光、驱动电压低、发光效率高、响应时间短、清晰度与对比度高、近180。视角、使用温度范围宽,可实现柔性显示与大面积全色显示等诸多优点,被业界公认为是最有发展潜力的显示装置

[0003]OLED按照驱动类型可分为无源OLED(PMOLED)和有源OLED(AMOLED)。其中,AMOLED通常是由低温多晶硅(Low Temperature Poly-Silicon,LTPS)驱动背板和电激发光层组成自发光组件。低温多晶硅具有较高的电子迁移率,对AMOLED而言,采用低温多晶硅材料具有高分辨率、反应速度快、高亮度、高开口率、低能耗等优点。

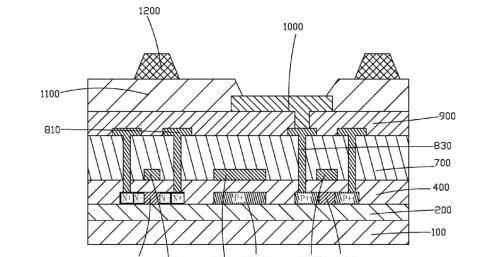

[0004]现有技术中常见的AMOLED背板的结构如图1所示。该AMOLED背板的制作过程大体为:

[0005]步骤1、在基板100上沉积缓冲层200;

[0006 步骤2、在缓冲层200上沉积非晶硅(a-Si)层,经激光(Laser)处理使非晶硅层结晶、转变为多晶硅(Poly-Si)层:接着通过黄光、蚀刻制程对多晶硅层进行图案化处理,形成间隔排列的第一多晶硅段301、第二多晶硅段303、及第三多晶硅段305;

[0007]步骤3、沉积栅极绝缘层400;

[0008]步骤4、通过黄光制程在栅极绝缘层400上制作第一层光刻胶图案;

[0009]步骤5、以第一光刻胶图案为遮蔽层对图案化的多晶硅层进行P型重掺杂,在第二多晶硅段303的两侧、及第三多晶硅段305形成P型重掺杂区域P+;

[0010]步骤6、先清除第一层光刻胶图案,再通过黄光制程在栅极绝缘层上制作第二层光刻胶图案:

[0011]步骤7、以第二层光刻胶图案为遮蔽层,对图案化的多晶硅层进行N型重掺杂,在第一多晶硅段301的两侧形成N型重掺杂区域N+;

[0012]步骤8、清除第二层光刻胶图案,在栅极绝缘层400上沉积并图案化第一金属层,形成第一栅极601、第二栅极605、及电极板603;

[0013]步骤9、以图案化的第一金属层作为遮蔽层对图案化的多晶硅层进行离子植入

(Self-align),在第一多晶硅段301的两侧形成轻掺杂漏极区域(Light Doping Drain)N-。

[0014]步骤10、在栅极绝缘层400上依次形成层间绝缘层700、第一与第二源/漏极810830、平坦层900、阳极1000、像素定义层1100、及光阻间隙物1200.

[0015]第一源/漏极810电性连接于第一多晶硅段301的N型重掺杂区域N+,第二源/

漏极830电性连接于第二多晶硅段303的P型重掺杂区域P+;阳极1000电性连接于第二源/漏极830

[0016]所述第一多晶硅段301、第一栅极601与第一源/漏极810构成开关TFT;第二多晶硅段303、第二栅极603与第二源/漏极830构成驱动TFT;第三多晶硅段305与电极板605构成存储电容。

[0017]通过上述方法制作AMOLED的背板存在一定的问题,若进行N型重掺杂之前的步骤6中的黄光制程偏移,容易造成位于开关TFT沟道区域两侧的轻掺杂漏极区域不对称。

发明内容

[0018]本发明的目的在于提供一种AMOLED背板的制作方法,能够使得开关TFT沟道区域两侧的轻掺杂漏极区域对称,增大导通电流,降低光电流,且节省一道光罩,降低成本。

[0019]为实现上述目的,本发明提供一种AMOLED背板的制作方法:依次在基板上沉积缓冲层、非晶硅层,使非晶硅层结晶、转变为多晶硅层并图案化多晶硅层,沉积栅极绝缘层后,先利用黄光制程制作的光刻胶图案为遮蔽层,对图案化的多晶硅层进行P型重掺杂;再在栅极绝缘层上沉积并图案化第一金属层,形成栅极,以图案化的第一金属层为遮蔽层对图案化的多晶硅层进行N型轻掺杂;然后沉积一层绝缘层,对该绝缘层进行非等向性蚀刻,形成阻隔物,再以图案化的第一金属层与阻隔物为遮蔽层对图案化的多晶硅层进行N型重掺杂,形成对称的轻掺杂漏极区域。

[0020]所述的AMOLED背板的制作方法具体包括如下步骤:

[0021]步骤1、提供一基板,在该基板上沉积缓冲层;

[0022]步骤2、在缓冲层上沉积非晶硅层,并对非晶硅层进行准分子激光退火处理,使得该非晶硅层结晶、转变为多晶硅层;再对多晶硅层进行图案化处理,形成相互间隔的第一多晶硅段、第二多晶硅段、及第三多晶硅段;

[0023]所述第三多晶硅段位于第一多晶硅段与第二多晶硅段之间;

[0024]步骤3、在所述缓冲层与第一、第二、第三多晶硅段上沉积栅极绝缘层;

[0025]步骤4、通过黄光制程在栅极绝缘层上制作光刻胶图案,该光刻胶图案完全遮蔽第一多晶硅段,遮蔽第二多晶硅段的中部,完全不遮蔽第三多晶硅段;

[0026]步骤5、以所述光刻胶图案为遮蔽层,对图案化的多晶硅层进行P型重掺杂,从而在第二多晶硅段的两侧、及第三多晶硅段形成P型重掺杂区域;

[0027]步骤6、清除所述光刻胶图案,在栅极绝缘层上沉积并图案化第一金属层,形成第一栅极、第二栅极及电极板;

[0028]所述第一栅极位于第一多晶硅段中部的上方;

[0029]步骤7、以图案化的第一金属层为遮蔽层对图案化的多晶硅层进行N型轻掺杂,从而在未被第一栅极遮蔽的第一多晶硅段的两侧形成N型轻掺杂区域;

[0030]步骤8、在所述栅极绝缘层与第一栅极、第二栅极及电极板上沉积一层绝缘层,再对该绝缘层进行非等向性蚀刻,形成阻隔物;

[0031]位于所述第一栅极两侧的阻隔物对称;

[0032]步骤9、以图案化的第一金属层与阻隔物为遮蔽层对图案化的多晶硅层进行N型重掺杂,从而在第一栅极的两侧于阻隔物的正下方形成对称的轻掺杂漏极区域;

[0033 步骤10、在栅极绝缘层上依次通过沉积、黄光、蚀刻制程形成层间绝缘层、第一与第二源/漏极、平坦层、阳极、像素定义层、及光阻间隙物;

[0034]所述第一源/漏极电性连接于第一多晶硅段的N型重掺杂区域,所述第二源/漏极电性连接于第二多晶硅段的P型重掺杂区域;所述阳极电性连接于第二源/漏极;

[0035]所述第一多晶硅段、第一栅极与第一源/漏极构成开关TFT:所述第二多晶硅段、第二栅极与第二源/漏极构成驱动TFT;所述第三多晶硅段与电极板构成存储电容。

[0036]所述绝缘层为富氧化硅层或富氮化硅层。[0037]所述绝缘层的厚度为0.2~0.5um。[0038]所述P型重掺杂的浓度高于N型重掺杂的浓度

[0039]所述缓冲层为氧化硅层、氮化硅层、或二者的组合。

[0040]所述层间绝缘层为氧化硅层、氮化硅层、或二者的组合。

[0041]所述第一栅极、第二栅极及电极板的材料为Mo。

[0042]所述第一与第二源/漏极的材料为Ti/Al/Ti.

[0043]所述阳极的材料为1TO/Ag/ITO.

[0044]本发明的有益效果:本发明提供的一种AMOLED背板的制作方法,在图案化第一金属层形成第一栅极、第二栅极及电极板后,以图案化的第一金属层为遮蔽层对图案化的多晶硅层进行N型轻掺杂;再沉积绝缘层,对绝缘层进行非等向性蚀刻,形成阻隔物,以图案化的第一金属层与阻隔物为遮蔽层对图案化的多晶硅层进行N型重掺杂,从而在第一栅极

的两侧于阻隔物的正下方形成轻掺杂漏极区域,一方面能够使得开关TFT沟道区域两侧的轻掺杂漏极区域对称,可缩短轻掺杂漏极区域的长度,增大导通电流,一方面由于阻隔物的材料为可以吸收光的富氧化硅或富氮化硅,能够有效降低光电流,且节省一道形成N型重掺杂区域的光罩,降低成本。

[0045]为了能更进一步了解本发明的特征以及技术内容,请参阅以下有关本发明的详细说明与附图,然而附图仅提供参考与说明用,并非用来对本发明加以限制。

附图说明

[0046]下面结合附图,通过对本发明的具体实施方式详细描述,将使本发明的技术方案及其它有益效果显而易见。[0047]附图中,

[0048]图1为现有AMOLED背板的结构示意图

[0049]图2为本发明AMOLED背板的制作方法的流程图;

[0050]图3为本发明AMOLED背板的制作方法的步骤2的示意图

[0051]图4为本发明AMOLED背板的制作方法的步骤3的示意图:[0052]图5为本发明AMOLED背板的制作方法的步骤4的示意图;[0053]图6为本发明AMOLED背板的制作方法的步骤5的示意图;[0054]图7为本发明AMOLED背板的制作方法的步骤6的示意图;

[0052]图5为本发明AMOLED背板的制作方法的步骤4的示意图;

[0053]图6为本发明AMOLED背板的制作方法的步骤5的示意图;

[0054]图7为本发明AMOLED背板的制作方法的步骤6的示意图;

[0055]图8为本发明AMOLED背板的制作方法的步骤7的示意图;

[0056]图9为本发明AMOLED背板的制作方法的步骤8中沉积绝缘层的示意图;

[0057]图10为本发明AMOLED背板的制作方法的步骤8中形成阻隔物的示意图;

[0058)图11为本发明AMOLED背板的制作方法的步骤9的示意图;

[0059]图12为本发明AMOLED背板的制作方法的步骤10的示意图。

具体实施方式

0060]为更进一步阐述本发明所采取的技术手段及其效果,以下结合本发明的优选实施例及其附图进行详细描述。

0061]请参阅图2,本发明提供一种AMOLED背板的制作方法,具体包括如下步骤

[0062]步骤1、提供一基板1,在该基板1上沉积缓冲层2。

0063]所述基板1为透明基板,优选的,所述基板1为玻璃基板或塑料基板。

0064]所述缓冲层2为Si0x氧化硅层、SiNx氮化硅层、或二者的组合。

0065]步骤2、如图3所示,在缓冲层2上沉积非晶硅层,并对非晶硅层进行准分子激光退火处理,使得该非晶硅层结晶、转变为多晶硅层:再对多晶硅层进行图案化处理,形成相互间隔的第一多晶硅段31、第二多晶硅段33、及第三多晶硅段35

[0066]所述第三多晶硅段35位于第一多晶硅段31与第二多晶硅段33之间。

0067]步骤3、如图4所示,在所述缓冲层2与第一、第二、第三多晶硅段31.33.35上沉积栅极绝缘层40068]步骤4、如图5所示,通过黄光制程在栅极绝缘层4上制作光刻胶图案5

[0068]步骤4、如图5所示,通过黄光制程在栅极绝缘层4上制作光刻胶图案5.

[0069]该光刻胶图案5完全遮蔽第一多晶硅段31,遮蔽第二多晶硅段33的中部,完全不遮蔽第三多晶硅段35

[0070]步骤5、如图6所示,以所述光刻胶图案5为遮蔽层,对图案化的多晶硅层进行P型重掺杂,从而在第二多晶硅段33的两侧、及第三多晶硅段35形成P型重掺杂区域P+

[0071]由于光刻胶图案5完全不遮蔽第三多晶硅段35,经P型重掺杂后,该第三多晶硅段35的导电性能大幅提高。

[0072]步骤6、如图7所示,清除所述光刻胶图案5,在栅极绝缘层4上沉积并图案化第一金属层,形成第一栅极61、第二栅极63及电极板65

[0073]具体的,所述第一栅极61位于第一多晶硅段31中部的上方,所述第二栅极63位于第二多晶硅段33中部的上方,所述电极板65与第三多晶硅段35相对应。所述第一栅极61、第二栅极63及电极板65的材料为钼Mo.

[0074]步骤7、如图8所示,以图案化的第一金属层即第一栅极61、第二栅极63及电极板65为遮蔽层对图案化的多晶硅层进行N型轻掺杂,从而在未被第一栅极61遮蔽的第一多晶硅段31的两侧形成N型轻掺杂区域N-。

[0075]步骤8、如图9、图10所示,首先在所述栅极绝缘层4与第一栅极61、第二栅极63及电极板65上沉积一层绝缘层7,所述绝缘层7的厚度为0.2~0.5um,其材料为富氧化硅

(Silicon rich oxide,SRO)或富氮化硅(Silicon rich nitride,SRN):再对所述绝缘层7进行非等向性蚀刻(Non-Isotropic etch),形成阻隔物71,所述阻隔物71分别位于第一栅极61、第二栅极63、与电极板65的两侧。

[0076]位于所述第一栅极61两侧的阻隔物71对称。

[0077]步骤9、如图11所示,以图案化的第一金属层与阻隔物71为遮蔽层对图案化的多品硅层进行N型重掺杂,从而在第一栅极61的两侧于阻隔物71的正下方形成轻掺杂漏极区域N-,在轻掺杂漏极区域N-的外侧形成N型重掺杂区域Nt.

[0078]由于位于所述第一栅极61两侧的阻隔物71对称,从而在第一栅极61的两侧于阻

隔物71的正下方形成的轻掺杂漏极区域N-也是对称的。

[0079]值得一提的是,该步骤9中N型重掺杂的浓度小于步骤5中P型重掺杂的浓度,N型重掺杂对第二多晶硅段33两侧的P型重掺杂区域P+的导电性能的影响较小。

0080]步骤10、如图12所示,通过沉积、黄光、蚀刻制程在栅极绝缘层4上依次形成层间绝缘层8、第一与第二源/漏极91.93、平坦层10、阳极11、像素定义层12、及光阻间隙物13

[0081]所述第一源/漏极91电性连接于第一多晶硅段31的N型重掺杂区域N+,所述第二源/漏极93电性连接于第二多晶硅段33的P型重掺杂区域P+;所述阳极11电性连接于第二源/漏极93.

[0082]所述第一多晶硅段31、第一栅极61与第一源/漏极91构成开关TFT;所述第二多晶硅段33、第二栅极63与第二源/漏极93构成驱动TFT;所述第三多晶硅段35与电极板65构成存储电容。所述存储电容位于开关TFT与驱动TFT之间。

0083]具体的,所述层间绝缘层8为Si0x氧化硅层、SiNx氮化硅层、或二者的组合。

0084]所述第一与第二源/漏极91、93的材料为钛/铝/钛Ti/Al/Ti.

0085]所述阳极的材料为氧化钢锡/银/氧化锡ITO/Ag/ITO.

0086]上述AMOLED背板的制作方法,由于开关TFT沟道区域两侧的轻掺杂漏极区域N-对称,可缩短轻掺杂漏极区域N-的长度,增大导通电流:由于构成阻隔物71的富氧化硅或富氮化硅可以吸收光,能够有效降低光电流;且N型重掺杂区域N+以图案化的第一金属或富氮化硅可以吸收光,能够有效降低光电流:且N型重掺杂区域N+以图案化的第一金属层与阻隔物71为遮蔽层,相比现有方法中采用黄光制程形成的光刻胶图案为遮蔽层,节省了一道光罩,能够降低成本。

[0087]综上所述,本发明的AMOLED背板的制作方法,在图案化第一金属层形成第一栅极、第二栅极及电极板后,以图案化的第一金属层为遮蔽层对图案化的多晶硅层进行N型轻掺杂:再沉积绝缘层,对绝缘层进行非等向性蚀刻,形成阻隔物,以图案化的第一金属层与阻隔物为遮蔽层对图案化的多晶硅层进行N型重掺杂,从而在第一栅极的两侧于阻隔物的正下方形成轻掺杂漏极区域,一方面能够使得开关TFT沟道区域两侧的轻掺杂漏极区域对称,可缩短轻掺杂漏极区域的长度,增大导通电流,一方面由于阻隔物的材料为可以吸收光的富氧化硅或富氮化硅,能够有效降低光电流,且节省一道形成N型重掺杂区域的光罩,降低成本。

[0088]以上所述,对于本领域的普通技术人员来说,可以根据本发明的技术方案和技术构思作出其他各种相应的改变和变形,而所有这些改变和变形都应属于本发明权利要求的保护范围。

本文内容由小余整理编辑!