在微电子电路设计中如何选择合适的电容?

当你在选择电容时,面对形形色色的该如何选择呢?

笔者分别来谈一谈常见的一些电容和其普遍的适用范围。注意:电容种类实在太多,所以这里只会涉及微电子电路设计中常见电容的使用的。譬如那些什么可变电容,超级电容等等暂时先不会覆盖到。

Ceramic Capacitor(陶瓷电容-无极性电容):

Pros:低ESR,很好的高频特性,稳定性高,温度系数小。Cons:电容值相对较低(几pFto几十uF),脆弱易受损,电容值受电压影响较大

陶瓷电容几乎是目前使用最最多的一种电容,常见用于去耦,信号耦合和模拟滤波器设计等等。现在工艺越来越好,大容值的陶瓷电容也能买到,只不过价钱相对较高。现在通常PCB的密度很高尺寸小,尤其是消费电子,很少会再见到使用leadedcap,常用的封装目前来说几乎都是贴片的。由于制作工艺的限制,低ESR电容的容值一般不会太高。

Electrolytic capacitor(电解电容-有极性电容):

Pros:高容值,相对便宜,不易受损,电容值受电压影响小。Cons:高ESR,ESL,很差的高频特性,稳定性低,温度系数高

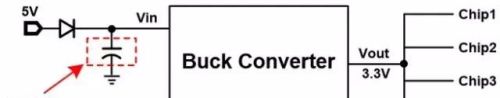

电解电容在电源电路里是很常见的,通常电容值比较大,从几个uF到几千uF的容值你都可以找的到。因为其高容值,高频特性差的特点(通常< 100kHz),常被用作输入电源的去耦稳压。要注意的是这里的电源不是指的芯片的Vdd或者Vcc,我所指的是比如你 PCB 的power总电源模块,例如一个5V的DC输入到一个Buck converter转成3.3V的DC给你PCB上其他各种芯片供电,通常电解电容是被接在这个5V电源和ground之间的。

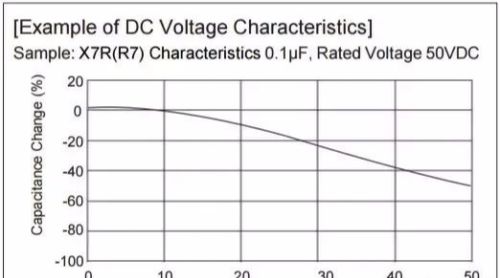

上图是我简单画的一个常用的电源模块设计,假如5V是整个PCB的总电源,一般这个电源后面放的去耦电容会使用电解电容,因为在这个位置我们通常不会太过多关注高频去耦,所以可以用相对较低的价钱得到一个较大的电容来去耦稳压。讲到这里,可能有人会问,我可以用陶瓷电容来替代这个电解电容吗?可以,也不可以。再解释这个之前,我们先来讲一下两种电容的容值v.s.电压的关系。看下图

这是我随便从Murata的一个陶瓷电容的datasheet上面截的一个电容变化v.s.电压的plot。很明显的可以看出来电容的值对于对其所加的电压不是一个恒定的值,也就是说对于上面这个电容,10V的时候电容值是0.1uF而电压变为50V时其实只有0.05uF。而电解电容的有点就在于它比陶瓷电容有更小的voltage dependency。其实电容值不仅仅会跟随电压变化而变化,还会根据温度的变化而变化,在这一点上电解电容是不如陶瓷电容的。从DFM(Design for manufacturability)和reliability的角度来说,电解电容一般都比较大,对于集成度超高的PCB很难fit进去。电解电容比陶瓷电容对物理损坏的抗性要高得多,尤其是在flex pcb上,陶瓷电容很容易受切损。但是在reliability上讲,陶瓷电容却又比电解电容要好。

电解电容其实是一个大类,常见的是铝电解电容。还有钽电解电容等等。比如钽电容,它改善了铝电解电容的一些缺点,其容值密度更高,有更好的高频特性,更reliable。但是!钽电容对于反向电压的容忍性极差,如果电压反向了或所加电压高于额定电压会很容易"爆"。

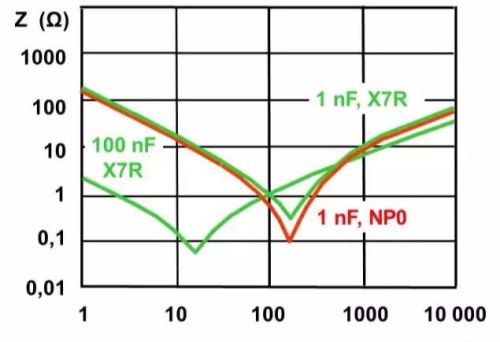

Decoupling Cap and PCB Layout

电容的频响特征,决定其频响特征的是ESR,ESL,和本身的C。在日常设计中,对layout比较critical的电容通常是去耦电容。常见的去耦电容使用都是一个大的+一个小的,因为容值小的电容普遍有更小的ESR,ESL,意味着在高频它整体看上去仍然会像一个电容而不是电感。这样的话就可以弥补大电容所覆盖不到的高频。正如下图所示,把一个100nF和一个1nF的阻抗频率特征曲线放在一起整体容性可以覆盖到将近200MHz,而单单100nF只能大概到20MHz。

所以最基本的PCB layout rule,把去耦电容放的离你芯片的pin越近越好,因为要保证PCB trace的寄生电阻,电感最小,这不仅仅是从Power到电容,还包括电容到ground!其次,放置电容时要远离噪声高的或者高频数字信号的线路。

对于微电子设计,可以说这两类电容几乎覆盖了平时所用到电容的90%以上。(其实我目前为止也很少接触其他种类电容)。当然了,如果你有兴趣了解其他电容,网上有很多信息可以去看,无非就是性能上的差别。关键在于设计时要把之前所提到不同电容的优点和缺点考虑进去,想想这些优缺点加进去会对你的电路造成什么样的影响?影响具体是多少?想明白了你才能做出正确的决定,从而选到一个最合适的电容。

1。为什么容值较大的陶瓷电容在加上电压工作时会发出声音?比如DC-DC converter的output capacitor。

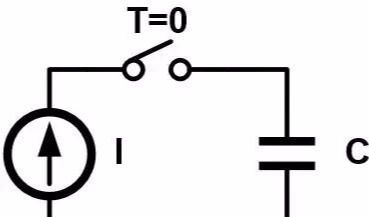

2。如下图所示,电容C是一个常见的陶瓷电容(非理想器件),容值为C=100nF,ESR=30mΩ,ESL=1nH,RatedVoltage为5V。电流源I为理想电流源。[Hints:请考虑一切可能发生的事情]

在T=0时开关关闭,请解释从T=0开始电容两端电压的变化,容值的变化。画出经过电容C的电流和两端的电压相对于时间的曲线。 如果下图理想电流源换成理想电压源V=3V,请问电容充电到99%需要多长时间?

还是使用理想电压源对这个电容C充电充到电压V1。根据公式,储存在电容上的总能量为E=\frac{1}{2}CV^{2},而C=\frac{Q}{V},所以E=\frac{1}{2}QV。但是理想电压源输出的总能量P=QV。为什么充电后到达电容C的能量只有一半?

再进阶一点问题,有什么方法可以将充电的能量损失降低到接近零?