电子电路之集电极开路、漏极开路等接口相关基本概念

1

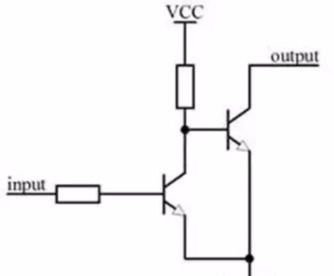

集电极开路输出

在电路中常会遇到漏极开路(Open Drain)和集电极开路(Open Collector)两种情形。漏极开路电路概念中提到的“漏”是指 MOSFET的漏极。同理,集电极开路电路中的“集”就是指三极管的集电极。在数字电路中,分别简称OD门和OC门。

典型的集电极开路电路如图所示。电路中右侧的三极管集电极什么都不接,所以叫做集电极开路,左侧的三极管用于反相作用,即左侧输入“0”时左侧三极管截止,VCC通过电阻加到右侧三极管基极,右侧三极管导通,右侧输出端连接到地,输出“0”。

从图中电路可以看出集电极开路是无法输出高电平的,如果要想输出高电平可以在输出端加上上拉电阻。因此集电极开路输出可以用做电平转换,通过上拉电阻上拉至不同的电压,来实现不同的电平转换。

用做驱动器。由于OC门电路的输出管的集电极悬空,使用时需外接一个上拉电阻Rp到电源VCC。OC门使用上拉电阻以输出高电平,此外为了加大输出引脚的驱动能力,上拉电阻阻值的选择原则,从降低功耗及芯片的灌电流能力考虑应当足够大;从确保足够的驱动电流考虑应当足够小。

将OC门输出连在一起时,再通过一个电阻接外电源,可以实现“线与”逻辑关系。只要电阻的阻值和外电源电压的数值选择得当,就能做到既保证输出的高、低电平符合要求,而且输出三极管的负载电流又不至于过大。

集电极开路输出除了可以实现多门的线与逻辑关系外,通过使用大功率的三极管还可用于直接驱动较大电流的负载,如继电器、脉冲变压器、指示灯等。

2

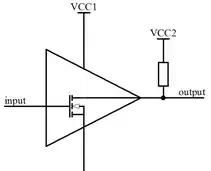

漏极开路输出

和集电极开路一样,顾名思义,开漏电路就是指从MOSFET的漏极输出的电路。典型的用法是在漏极外部的电路添加上拉电阻到电源如图所示。完整的开漏电路应由开漏器件和开漏上拉电阻组成。这里的上拉电阻R的阻值决定了逻辑电平转换的上升/下降沿的速度。阻值越大,速度越低,功耗越小。因此在选择上拉电阻时要兼顾功耗和速度。标准的开漏脚一般只有输出的能力。添加其它的判断电路,才能具备双向输入、输出的能力。

很多单片机等器件的I/O就是漏极开路形式,或者可以配置成漏极开路输出形式,如51单片机的P0口就为漏极开路输出。在实际应用中可以将多个开漏输出的引脚连接到一条线上,这样就形成“线与逻辑”关系。注意这个公共点必须接一个上拉电阻。当这些引脚的任一路变为逻辑0后,开漏线上的逻辑就为0了。在I2C等接口总线中就用此法判断总线占用状态。

同集电极开路一样,利用外部电路的驱动能力,减少IC内部的驱动。当IC内部MOSFET导通时,驱动电流是从外部的VCC流经上拉电阻,再经MOSFET到GND。IC内部仅需很下的栅极驱动电流,因此漏极开路也常用于驱动电路中。

3

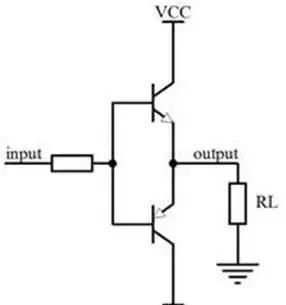

推挽输出

在功率放大器电路中经常采用推挽放大器电路,这种电路中用两只三极管构成一级放大器电路,如图所示。两只三极管分别放大输入信号的正半周和负半周,即用一只三极管放大信号的正半周,用另一只三极管放大信号的负半周,两只三极管输出的半周信号在放大器负载上合并后得到一个完整周期的输出信号。

推挽放大器电路中,一只三极管工作在导通、放大状态时,另一只三极管处于截止状态,当输入信号变化到另一个半周后,原先导通、放大的三极管进入截止,而原先截止的三极管进入导通、放大状态,两只三极管在不断地交替导通放大和截止变化,所以称为推挽放大器。输出既可以向负载灌电流,也可以从负载抽取电流

4

上拉电阻与下拉电阻

在嵌入式接口的相关应用中经常提到上拉电阻与下拉电阻,顾名思义,上拉电阻就是把端口连接到电源的电阻,下拉电阻就是把端口连接到地的电阻。虽然电路形式非常简单,然而上拉电阻与下拉电阻在很多场合却扮演着非常重要的作用。

简单的说,上拉电阻的主要作用在于提高输出信号的驱动能力、确定输入信号的电平(防止干扰)等,具体的表现为:

l 当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V), 这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。

l OC门电路必须加上拉电阻,以提高输出的搞电平值。

l 为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。

l 在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。

l 芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。

l 提高总线的抗电磁干扰能力。管脚悬空就比较容易接受外界的电磁干扰。

l 长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。

上拉电阻阻值的选择原则包括:

l 从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。

l 从确保足够的驱动电流考虑应当足够小;电阻小,电流大。

l 对于高速电路,过大的上拉电阻可能边沿变平缓。

综合考虑以上三点,通常在1K到10K之间选取。对下拉电阻也有类似道理。

5

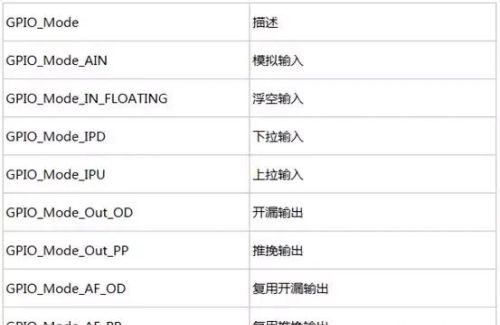

嵌入式微控制器的I/O配置

上面介绍了嵌入式系统接口设计中相关的接口电路和概念,嵌入式微控制器的I/O是在嵌入式系统设计中最常用到的接口,很多微控制器的I/O口可以进行灵活配置,以本书中介绍的STM32F10X为例,STM32F10X的I/O可以配置成如表中所示的8中模式。因此在I/O的应用中更为灵活。

STM32F10X端口位的基本结构如图所示,从图中可以看到典型的推挽输出电路与上下拉电阻,当N-MOS被激活时就变成了典型的开漏输出模式,当N-MOS和P-MOS同时被激活时就变成了典型的推挽输出模式,通过上拉电阻和下拉电阻的开关控制可以使端口处于上拉或者下拉输入模式。

根据开漏输出和推挽输出的特点,可以很容易判断在以下应用中应当工作在推挽输出模式(或者复用推挽输出):

l 驱动应用中,驱动LED、蜂鸣器等

l USART_TX、USART_CK、USART_RTS、MOSI、SPI主模式SCK、CAN_TX等需要较强驱动能力的场合

而在I2C等接口总线应用中,由于需要“线与”判断总线占用状态,以及需要使用电平转换的场合需要将I/O配置成开漏输出的模式。