高速ADC为什么有如此多电源域

在采样速率和可用带宽方面,当今的射频模数转换器(RF ADC)已有长足的发展。其中还纳入了大量数字处理功能,电源方面的复杂性也有提高。那么,当今的RF ADC为什么有如此多不同的电源轨和电源域?

为了解电源域和电源的增长情况,我们需要追溯ADC的历史脉络。早在ADC不过尔尔的时候,采样速度很慢,大约在数十MHz内,而数字内容很少,几乎不存在。电路的数字部分主要涉及如何将数据传输到数字接收逻辑——专用集成电路 (ASIC) 或现场可编程门阵列 (FPGA)。用于制造这些电路的工艺节点几何尺寸较大,约在180 nm或更大。使用单电压轨(1.8 V )和两个不同的域(AVDD和DVDD,分别用于模拟域和数字域),便可获得足够好的性能。

随着硅处理技术的改进,晶体管的几何尺寸不断减小,意味着每 mm2面积上可以容纳更多的晶体管(即特征)。但是,人们仍然希望 ADC 实现与其前一代器件相同(或更好)的性能。

现在,ADC 的设计采取了多层面方法,其中:

1、采样速度和模拟带宽必须得到改善;

2、性能必须与前一代相同或更好;

3、纳入更多片内数字处理功能来辅助数字接收逻辑。

下面将进一步讨论上述各方面特性以及它们对芯片设计构成怎样的挑战。

需要高速度

在 CMOS 技术中,提高速度(带宽)的最普遍方法是让晶体管几何尺寸变小。使用更精细的 CMOS 晶体管可降低寄生效应,从而有助于提高晶体管的速度。晶体管速度越快,则带宽越宽。数字电路的功耗与开关速度有直接关系,与电源电压则是平方关系,如下式所示:

其中:

P为功耗

CLD 为负载电容

V 为电源电压

fSW 为开关频率

几何尺寸越小,电路设计人员能实现的电路速度就越快,而每MHz每个晶体管的功耗与上一代相同。以 AD9680 和 AD9695为例,二者分别采用65 nm和28 nm CMOS技术设计而成。在1.25 GSPS和1.3GSPS时,AD9680和AD9695的功耗分别为3.7 W和1.6 W。这表明,架构大致相同时,采用28 nm工艺制造的电路功耗比采用65 nm工艺制造的相同电路的功耗要低一半。因此,在消耗相同功率的情况下,28 nm工艺电路的运行速度可以是65 nm工艺电路的一倍。AD9208很好地说明了这一点。

裕量最重要

对更宽采样带宽的需求促使业界采用更精细的几何尺寸,不过对数据转换器性能(如噪声和线性度)的期望仍然存在。这对模拟设计提出了独特的挑战。转向更小几何尺寸的一个不希望出现的结果是电源电压降低,这使得开发模拟电路以工作在高采样速率并保持相同的噪声/线性度性能所需的裕量大大降低。为了克服这一限制,电路设计有不同的电压轨以提供所需的噪声和线性度性能。

例如在 AD9208中,0.975 V电源为需要快速切换的电路供电。这包括比较器和其他相关电路,以及数字和驱动器输出。1.9 V电源为基准电压和其他偏置电路供电。2.5 V电源为输入缓冲器供电,而要在高模拟频率下工作,裕量必须很高。没有必要为缓冲器提供2.5 V电源,它也可以工作在1.9 V。电压轨的降低会导致线性度性能下降。

数字电路不需要裕量,因为最重要的参数是速度。所以,数字电路通常以最低电源电压运行,以获取CMOS开关速度和功耗的优势。这在新一代ADC中很明显,最低电压轨已降低至0.975 V。下面的表1列出了若干代的一些常见ADC。

表1:产品比较

隔离是关键

随着业界转向深亚微米技术和高速开关电路,功能集成度也在提高。以 AD9467 和A D9208为例,AD9467采用180 nm BiCMOS工艺,而AD9208采用28 nm CMOS工艺。当然,AD9467的噪声密度约为-157 dBF S/Hz,而AD9208的噪声密度约为-152 dBF S/Hz。 但是,如果拿数据手册做一个简单的计算,取总功耗(每通道)并将其除以分辨率和采样速率,就可以看到A D9467的功耗约为330μW/位/MSPS,而AD9208仅为40μW/位/MSPS。

与AD9467相比,AD9208具有更高的采样速率(3 GSPS对250 MSPS)和高得多的输入带宽(9 GHz对0.9 GHz),并且集成了更多数字特性。A D9208可以完成所有这些工作,每位每MSPS的功耗只有大约1/8。每位每MSPS的功耗不是工业标准指标,其在本例中的作用是突出ADC设计中使用更小尺寸工艺的好处。当超快电路在非常近的距离内运行时,各个模块之间总会存在耦合或震颤的风险。

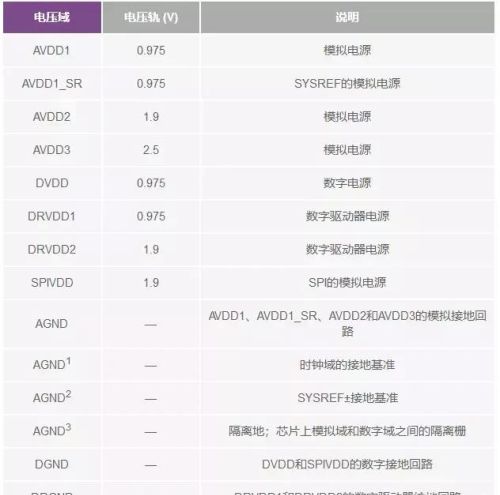

为了改善隔离,设计者必须考虑各种耦合机制。最明显的机制是通过共享电源域。如果电源域尽可能远离电路,那么共享同一电压轨(AD9208为0.975 V)的数字电路和模拟电路发生震颤的可能性将非常小。在硅片中,电源已被分开,接地也是如此。封装设计继续贯彻了这种隔离电源域处理。由此所得的同一封装内不同电源域和地的划分,如表2所示,其以AD9208为例。

表2:AD9208电源域和接地域

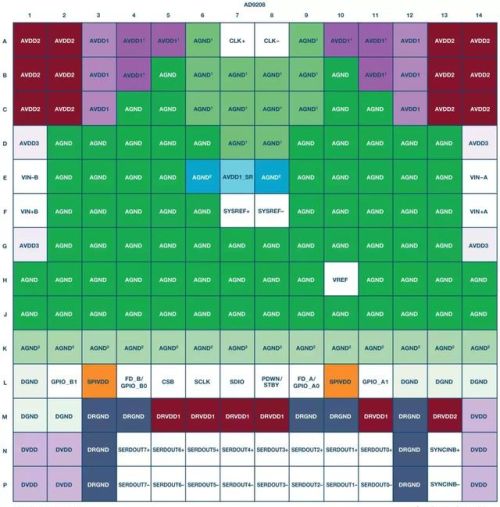

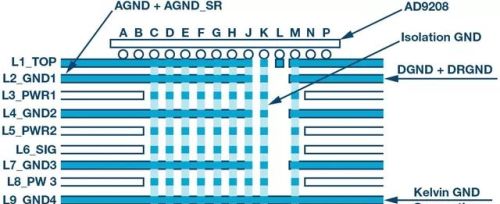

显示AD9208各不同域的引脚排列图如图1所示。

图1. AD9208引脚配置(顶视图)

这可能会让系统设计人员惊慌失措。乍一看,数据手册给人的印象是这些域需要分开处理以优化系统性能。

看不到尽头?

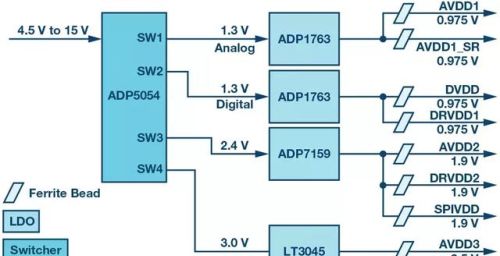

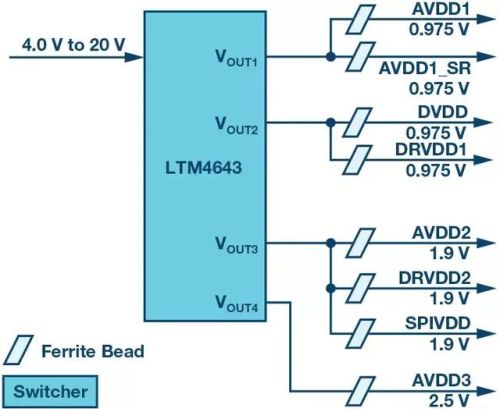

情况并不像看起来那么可怕。数据手册的目的仅仅是唤起人们对各种敏感域的关注,让系统设计人员可以关注PDN(电源输送网络)设计,对其进行适当的划分。共享相同供电轨的大多数电源域和接地域可以合并,因此PDN可以简化。这导致BOM(物料清单)和布局得以简化。根据设计约束,图2和图3显示了AD9208的两种PDN设计方法。

图2. AD9208引脚配置(顶视图)

图3. AD9208 PDN,DC-DC转换器为所有域供电

通过充分滤波和布局分离,各个域可以合理布置,使得ADC性能最大化,同时降低BOM和PDN复杂性。各接地域采用开尔文连接方法也会改善隔离。从网表角度来看,仍然只有一个GND网。电路板可以划分为不同接地域以提供充分的隔离。在AD9208的评估板AD9208-3000EBZ中,不同接地分区在第9层上形成开尔文连接。图4所示为10层PCB(印刷电路板)AD9208-3000EBZ的横截面,其显示了不同GND连接。

图4. AD9208下方的AD9208-3000 EBZ PCB横截面

所以,这不是世界末日?

绝对不是。仅仅因为AD9208数据手册显示了所有这些域,并不意味着它们在系统板上必须全部分离。了解系统性能目标和ADC目标性能对优化ADC的PDN起着重要作用。在电路板上使用智能分区以减少不必要的接地回路,是将各个域之间的串扰降到最低的关键。适当地共享电源域,同时满足隔离要求,将能简化PDN和BOM。