三总线的扩展设计方法

基本思路

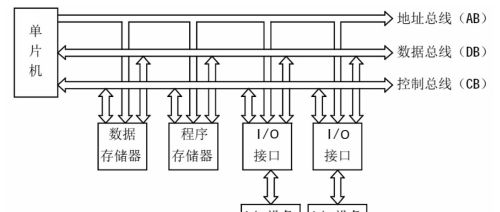

51系列单片机采用总线结构,使扩展易于实现,其扩展结构如图4-3所示。

图4-3 AT89S51单片机系统扩展结构图

由图4-3可以看出,系统扩展主要包括存储器扩展和I/O接口部件扩展。51系列单片机的存储器扩展既包括程序存储器扩展又包括数据存储器扩展。51系列单片机采用程序存储器空间和数据存储器空间截然分开的哈佛结构。扩展后,系统形成了两个并行的外部存储器空间。系统扩展是以51单片机为核心,通过总线把单片机与各扩展部件连接起来。因此,要进行系统扩展,首先要构造系统总线。系统总线按功能通常分为3组,如图4-3所示。

51单片机有4个8位的并行口,已占用了32条引线,而51单片机总共只有40条引脚,这8根数据线和16根地址线必须采用引脚复用的方法,也就是一根引脚必须有两种或更多种功能才能满足需要,某一根引脚究竟作何用,则需要根据硬件的要求进行设计,从而使用其不同的功能。

如何构造系统的三总线1. 数据总线

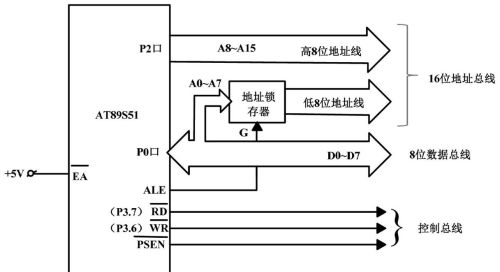

如图4-4所示为单片机的三总线结构形式。51单片机的P0口是一个多功能口,如果扩展外围芯片,P0口就可以作为数据总线和低8位的地址总线来使用。CPU先从P0口送出低8位地址,然后从P0口送出数据或接收数据。

图4-4 单片机的三总线结构形式

2. 地址总线

在51单片机访问外部存储器或I/O口时,可能需要超过8位的地址线,这时就用P2作为高8位的地址线。在P0口出现低8位地址信号时,P2口也出现高8位的地址线,这样共有16根地址线。

3. 控制总线

除地址线和数据线外,还要有系统的控制总线。这些信号有的是单片机引脚的第一功能信号,有的则是P3口第二功能信号。包括:

(1)作为外扩程序存储器的读选通控制信号。

(2)作为外扩数据存储器和I/O的读、写选通控制信号。

(3)ALE作为P0口发出的低8位地址锁存控制信号。

(4)为片内、片外程序存储器的选择控制信号。

可见,AT89S51的4个并行I/O口,由于系统扩展的需要,真正作为数字I/O使用,就剩下P1和P3的部分口线了。

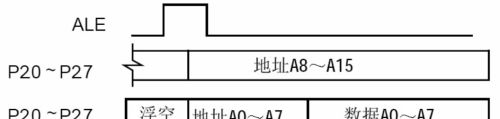

4. 地址、数据分离电路

单片机的P0口作为数据总线和低8位的地址总线使用,如果直接将P0口接到扩展芯片的数据总线和低8位地址线是行不通的,例如,单片机选定了外部存储器的0000H单元,P0、P2口就应当输出00H,这样才能选中0000H单元,在选中0000H单元后,就从这个单元读取数据,这个数据的值是随机的,假设这个数据是10H,P0口就变成了10,但这样就不再是选中0000H单元,而是选中了0010H单元,显然,这从逻辑上是讲不通的,所以P0口送出地址和接收或更新出数据是分时进行的,一定要把地址和数据区分开。

如图4-5所示是P0口的地址/数据复用关系,从图中可以看出,在每一个周期里,P2口始终是输出高8位的地址信号,而P0口却被分成两个时段,第一个时段输出低8位的地址,而第二个时段则是传输数据,为了要把低8位的地址信号提取出来,要用到一个锁存器芯片。从图4-5中还可以看出,在ALE的上升沿到来时,P0口是处于“浮空”状态,也说“高阻”状态,即构成P0口输出的两个晶体管均处于“截止”的状态,这样不会影响到锁存器。ALE信号就是MCS-51单片机提供的专用于数据/地址分离的一个引脚。

图4-5 P0口地址、数据复用示意图

对于片外数据存储器,单片机使用了与访问片内数据存储器不同的指令进行访问。此外,如果扩展了其他连接如I/O等芯片,也要占用RAM空间。