Veilog语法介绍之常量

任何一种计算机语言都离不开常量和变量。

Verilog HDL语言中描述电路的基本常量有4种,分为数值常量和非数值常量:

(1)0:代表逻辑0或“假”;

(2)1:代表逻辑1或“真”;

(3)x:表示不确定;

(4)z:表示高阻。

这4种值的解释都内置于Verilog HDL语言中。数值常量“0”和“1”在逻辑电路中被解释为低电位和高电位。如一个电路的值为z,则该电路处于高阻抗状态,也就是电路处于断开状态。一个电路的值为x,则该电路处于不确定的状态。在逻辑门电路的输入或一个逻辑表达式中,为“z”的值通常解释为电路断开,其他值都被解释为导通。此外,x值和z值不分大小写,也就是说,值x、z与值X、Z相同。

电路常量表示的是一条导线的状态,我们称其为导线的值。除了导线的基本电路常量之外,Verilog HDL程序设计中还使用整型数、实数和字符串型3类常量。这3类常量主要用于电路的辅助描述,在实际电路中并没有这3类数值。

整型数常用基数表示方法给出,这种表示法要求书写形式固定。书写整型常数时,前面要写出二进制的位数,跟着用“'”号将进制标识和数字隔开,接下来再书写该进制的数码。在整型数或实数的描述中可以使用下画线,符号“_”可以随意用在整型数或实数中,它们就数量本身而言没有意义。它们能用来提高易读性,唯一的限制是下画线符号不能用作为首字符。

例如,16'b0001001000111111 和 16'h1_23_f,它们分别表示 16 位的二进制数0001001000111111和16个二进制位的十六进制整数123f,用十进制实数表示就是4671。

Verilog HDL规定十进制实数与通常的写法一样。

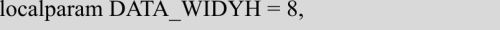

HDL代码经常在表达式和数组的边界使用常量。这些值在模块内是固定的,不可修改。一个很好的设计惯例是用符号常量取代这些hard literal,这样做可使代码清晰,便于后续维持及修改。在Verilog中,可以使用localparam(本地参数)来声明常量。例如,我们可以声明一个数据总线的位宽及数据范围为:

或者定义一个符号端口名称:

声明中的表达式,如2*DATA_WIDTH-1,在预编译时计算,因此它不会引用任何物理电路。一般使用大写字母来表示常量。

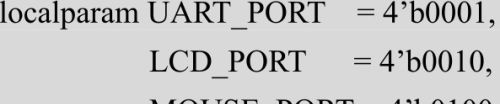

常量的使用可用实例来说明。考虑一个带进位的加法器的代码。为了正确执行加法运算,可将输入的值手动扩展1位,并取和的最高位为进位。代码如下:

代码1 使用hard literal的加法器

代码所示为4位加法器。hard literal,即硬文字,如用来表示数据范围的3和4、wire[4:]及sum_ext[3:0]以及最高位sum_ext[4]。如果需要把它修改为8位的加法器,那么就需要手动修改这些hard literal。如果代码很复杂且多处都引用这些hard literal,那么修改起来将是件痛苦的事情,同时也有可能带来不必要的错误。

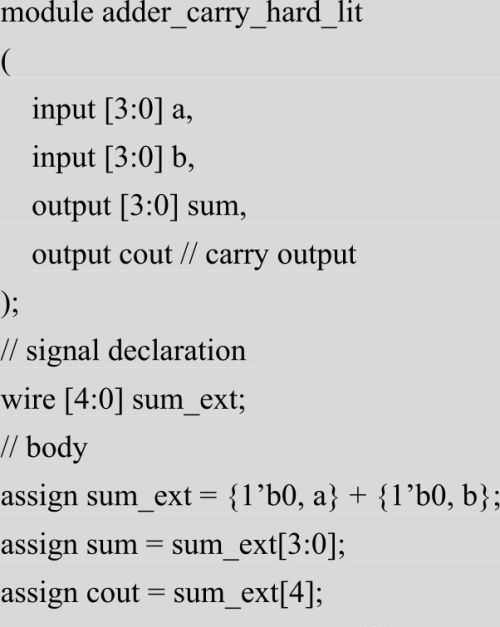

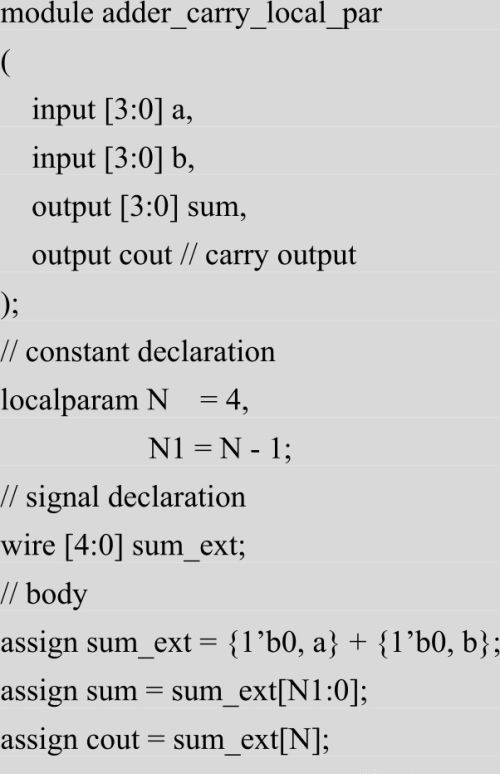

为了提高代码的可读性,我们可以使用符号常量,如用N来代表加法器的位数。修改后的代码如下所示:

代码2 使用常量的加法器

常量使代码更易于理解和维持。