详解状态机的设计

状态机通常要写成3段式,从而避免出现过大的组合逻辑。

如果设计中有一个几十个状态的状态机,它的状态译码逻辑将非常之巨大,毫无疑问,这极有可能是设计中的关键路径。那该怎么做呢?基本思路是减少组合逻辑。我们可以对状态的输出进行分析,对它们进行重新分类,并根据这个重新定义成多组小状态机,通过对输入进行选择(case语句)来触发相应的小状态机,从而实现了将大的状态机切割成小的状态机。在ATA6的规范中(硬盘的标准),输入的命令大概有二十几种,每一个命令又对应很多种状态,如果用一个大的状态机(状态套状态)去做那是不可想象的,可以通过case语句对命令进行译码,并触发相应的状态机,这样做下来这一个模块的频率就可以跑得比较高了。

设计状态机时,对于所有的输出信号在每一个时钟周期的取值,都必须有非常明确的定义。也就是说在每一个状态周期里面,对每一个输出值在该状态可能的各种情况下,都必须赋予明确的值。否则,综合结果会多很多不必要的门。

这是因为由于没有在每一个状态周期里面给输出信号赋值,因而需要有硬件来维持原来的输出信号值保持不变。综合工具解决的唯一办法是把输出信号值反馈给多路选择器,当某一时钟周期没有给输出信号赋值时,多路选择器再把这个值送给输出信号,使得输出信号值得以维持不变。(这就是锁存LATCH效应)

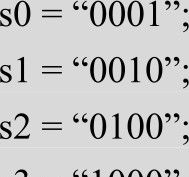

关于e-hot状态机编码1)one-hot编码

每一个状态用掉一个触发器,状态数等于触发器的数目。这就意味着触发器数目增加,而状态译码组合电路被优化掉了。对于寄存器资源丰富的xilinx器件来说,是非常适合的。

2)one-hot状态机的好处

(1)对寄存器资源丰富xilinx fpga来说更易于适配和布线。

(2)one-hot状态机是典型的相当快速的状态机。它的速度与状态的个数没有任何关系,仅仅取决于状态变迁到一个特殊状态的这种转换的数量。

(3)不用担心你会在发现最佳的状态机编码方式。因为其他设计的状态机如果再加入一些状态或者改变其他一些什么的话,那就可能不再是最优了。one-hot编码方式在所有状态机中是最佳的、最优的。

(4)one-hot状态机很容易设计。状态图能够直接被画成原理图或者直接用硬件描述写出来,而不用编码成状态表。

(5)修改起来简单明了。综合器能很容易地增加和删掉一些状态或者改变一些敏感量等式,而不会影响余下的状态机。

(6)很容易从vhdl或者verilog综合。

(7)与其他一些高性能的状态机相比没有任何的布线面积的浪费。

(8)能够用静态时序分析的方法很容易地找出危险的不合理的状态机转换路径。

温馨提示加入圈子,即可获取更多相关资料,终身会员制,不再收取第二次费用,赶紧加入我们吧!