电路原理图设计的EMC风险评估/分析一

产品电路原理图的设计是产品设计的核心,对原理图设计的EMC风险评估(分析) 目的是为了指出现有原理图存在的EMC问题,通过EMC设计风险分析及修改,最大限 度地降低EMC风险,降低设计成本。在这个阶段,产品的构架基本已定型,因此共模电流的路径也基本确定,在此基础上来考虑电路原理的设计,进一步降低函C风险,同时,随之提出的PCB布局布线建议也将降低PCB设计的EMC风险和设计成本。参与人员通常包括EMC专家、系统工程师、电子硬件工程师、CAD工程师。

电路原理图的EMC风险评估(分析)是建立在对原理图中的电路进行划分的基础上 的,通过分析将电路原理图分成:

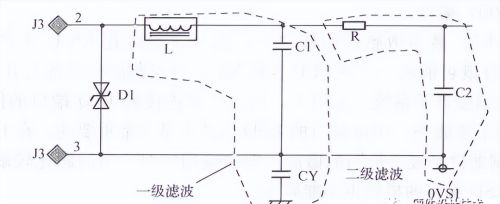

“脏”的部分“干净”的部分滤波、去耦的部分需要做特殊处理的部分电路原理图的EMC风险评估(分析)原理,其中“脏”或噪声区域部 分通常是电路中的I/O部分或产品的壳体。在这些I/。端口或壳体上需要进行EMC测 试,EMC干扰需要从这些I/O 口注入,这些电路是产品中受干扰最严重、最直接的部 分。如产品的ESD放电点、电源端口的电路,通信端口的电路,其他输入/输岀口的电路。通常,这些电路不能直接延伸到内部干净的电路区域,其间需要包含至少具有一个以 上器件(如电容)组成的滤波器或滤波电路与其配合使用,滤波电路包括共模滤波和差模 滤波。对于接地产品,共模滤波是必须的。在有些不能使用共模滤波的情况下(如产品浮 地),除了 I/O端口需要进行差模滤波外,还要在PCB设计时保证共模电流干扰路径上地 平面的完整,以降低共模电流流过时产生的压降,不然就需要在地阻抗较高区域的信号线 上加电容进行差模滤波。

“干净”区域的电路部分是不会受外接直接干扰或内部噪声源干扰的部分电路。在 电路中其通常位于滤波电路之后,也是电路中需要保护的部分,如A/D -D/A转换电路、检测电路、CPU核心电路等。滤波、去耦及隔离区域部分是介于“干净”电路部分与“脏”电路部分之间的、完成 对“干净"电路和“脏”电路隔离的电容或其他PCB设计措施,它是为了保护“干净” 的电路不受外界干扰的影响,并将干扰滤除,或将产品内部特殊噪声电路或敏感电路“隔 离”在其他电路之外。滤波电路通常至少由一个或多个电容组成,往往还会包括电感、磁 珠、电阻等器件。

内部噪声电路、敏感电路的区域是一些需要做特殊处理的部分,它是电路中比较特殊的部分。通常特殊电路包括两种电路,第一种是极其敏感的电路(如复位电路、低电压、 低电流检测电路、低电压模拟电路、高输入阻抗电路等),这些电路不像其他普通数字电 路一样具有相对较高的抗干扰能力。对于这些敏感电路,除了进行像普通电路一样滤波去 耦处理之外,还有必要进行一些额外处理,如二级滤波、屏蔽、对其信号线进行包地等处 理。第二种是内部电路的噪声源(如电路中的晶振和时钟电路,开关电源中的开关管、开 关回路)。由辐射形成原理的描述可知,形成辐射的必要条件是辐射噪声源与天线。对这部分电路的处理主要是为了降低噪声源的电平,并将其隔离于“天线”之外, 通常需要做特殊处理,常用的措施有屏蔽、去耦、对其信号线进行包地等,使其与其他信 号线和电路之间不发生串扰,以免噪声传输复杂化。

在PCB布线布局的时候,各个电路部分之间的串扰是着重需要考虑的,避免串扰的方法,在后续文章中进行描述。

该内容转载自硬件设计技术,仅供学习交流使用,如有侵权,请联系删除。