晶振常用输出波形解析及应用

对电路设计工程师而言,晶振是一种非常常见的电子元器件,特别是在数字电路的应用场景里,晶振的知识可以从很多角度去延伸和展开。

本文将从晶振的输出波形和应用场景展开,让您更进一步的了解和认识晶振,从而更好的完成相关设计,充分发挥出晶振特有的效能,最大地实现晶振的价值,根据实际的应用场景和晶振输出波形选择合适的晶振。

晶振到底有哪些输出波形呢?常用的输出波形主要是方波、正弦波和削顶正弦波。而方波又由于其具体的实现原理、参数或具体输出端的不同而细分为很多波形。下面我们来具体看看各种不同的波形及其各自的特点:

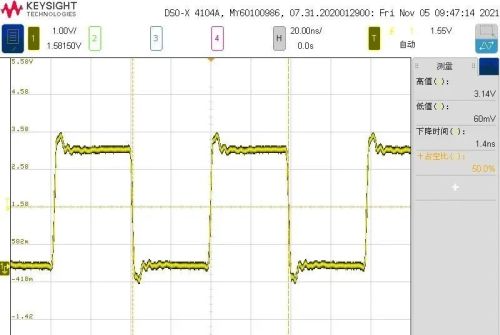

方波

方波(Square Wave),是各种波形中家族成员最多的一个,应用的场景也很多,但其有一个最大的问题是其谐波分量非常的丰富,实际使用中,综合考虑时钟沿抖动和谐波干扰的影响,能满足系统抖动要求的前提下,尽量使信号沿缓一些。

单端方波:

TTL(Transistor-Transistor Logic):即晶体管-晶体管逻辑电路,其传输延迟快,功耗高,而且顾名思义,其属于电流控制型的器件,最高频率可达100MHz,抖动性能一般。CMOS(Complementary Metal Oxide Semiconductor):即互补金属氧化物半导体CMOS逻辑电路,其主要特点是传输延迟时间慢,功耗低,从实现原理来看,属于电压控制性器件。相对于TTL而言,其噪声容限更高,输入阻抗也远大于TTL的输入阻抗,最高频率可达200MHz,抖动性能一般。HCMOS(High speed CMOS):即高速CMOS,除集成了CMOS几乎所有的特点外,HCMOS的速度要比CMOS的速度更快。差分信号:

ECL(Emitter Coupled Logic):即发射极耦合逻辑电路,它的主要特点是速度快、驱动能力强、噪声小,最高频率可达2.1GHz,抖动指标也很好,但缺点是功耗很大,而且还需要负电源。PECL(Positive ECL):即正发射极耦合逻辑电路,其是在ECL的基础上改进而来,因为ECL除了正电源外还需要一个负电源,有时会给设计带来不便,因此诞生了PECL。LVPECL(Low Voltage PECL):是在PECL的基础上改进而来,典型输出为一对差分信号,发射极通过交流源接地。需要注意的是:ECL、PECL和LVPECL均为发射极跟随输出结构,必须有电阻拉到一个直流偏置电压。当然,关于具体的电路设计属于另外一个话题的范畴,我们就不在这里展开。LVDS(Low Voltage Differential Signaling):即低压差分信号,频率可以达到600MHz以上,应用模式主要有三种:1、单向点对点和双向点对点;2、多分支形式;3、多点结构。其整体对PCB的设计要求较高,差分线要严格等长等,所以在具体设计时要特别注意。正弦波

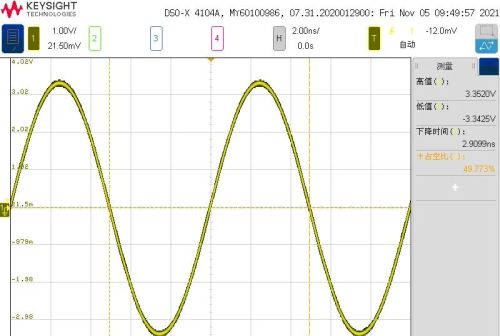

正弦波(Sine Wave),一般负载为50Ω。相对方波而言,其谐波分量要少很多,一般谐波抑制均可优于-30dB。缺点是信号沿比较缓慢,在噪声的影响下,相位准确度会变差,不适合做数字系统的参考时钟。

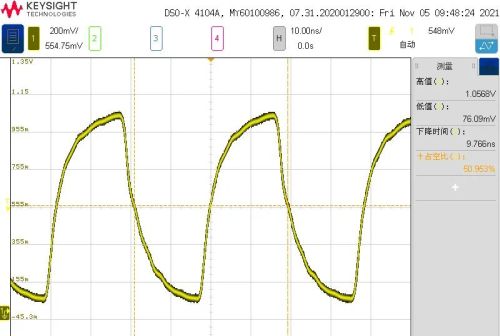

削顶正弦波

削顶正弦波(Clipped Sine Wave),谐波分量相比方波较小,但驱动能力也较弱。在负载为10kΩ//10pF时,Vp-p为0.8Vmin,通常小型化表贴TCXO会输出该波形,信号沿介于正弦波和方波之间。

现在我们已经完成了各种波形的梳理,接下来的问题是这么多波形,我们应该怎么选择呢?换个角度说,也就是这么多种类的波形,分别会使用在什么样的场景里呢?

正弦波

由于正弦波其自身的特点,决定了其通常用于射频信号处理、频率源等应用场合。比如要驱动同轴电缆将时钟信号进行长线传输时、要驱动滤波器类的电路时,或者为实现整形放大等目的作为三极管和高速运放的输入时。正弦波均是最适合的波形。而且,更为重要的是,由于正弦波谐波分量很少,因此当对EMI、频率干扰等有特殊要求时,例如微波通信、雷达和高速数传等类似系统,正弦波是不二的选择。

削顶正弦波

关于削顶正弦波,主要应根据实际应用对谐波、功耗、成本以及具体电路的适配性来选择。因为削顶正弦波的低功耗特性,使其改善了热特性和频率稳定性能,所以当对这些指标以及成本有考量时,可以考虑削顶正弦波。

方波

方波是工程师接触最多的时钟波形,主要应用在数字通信系统时钟上,用来驱动相关电路。比如驱动门电路时,由于门电路要讲究严格的高低电平、占空比、上升/下降沿时间等指标,此时方波是最好的选择。而且再进一步来讲,门电路的电平也是分为不同的种类,也要据此来进行进一步的判断。当然,现在也是有可以兼容的情况,这些就需要工程师们自己来具体把握了。