开关电源芯片注意事项

一颗芯片从寻找市场需求,功能定义,设计工程师功能实现,芯片layout,至代工厂流片,生产周期长,且成本较高。在前端芯片功能定义时,需要仔细地考虑芯片的工作条件和运行状态,使芯片、以及芯片所作用的器件甚至整个样机,都工作在一个确定可控的状态。下面介绍开关电源中,芯片功能定义较常出现的问题。

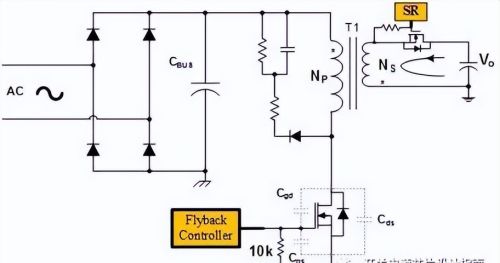

功率开关管耦合误开:功率开关器件的漏极,栅极和源极存在极间寄生电容,如下图所示,分别为Cgd, Cgs和Cds。

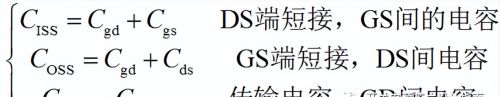

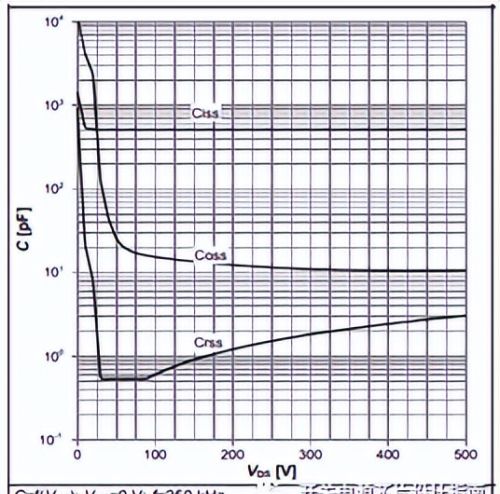

在MOS管数据手册中,通常由以下三个参数来进行量化,如下图所示。极间电容关系如下式,在 MOS管VDS较高时,Cgs要比Cgd大得多;当VDS较低时,结电容的容值将迅速增加。

当控制芯片对功率管门极驱动浮空时,门极电压VGS有可能被高速变化的VDS通过Cgd耦合起来。但通常情况下,由于Cgs相对Cgd较大,VGS被耦合的电压较低,且门极开启电压较高,MOS管不容易误开。但随着逻辑电平MOS(开启电压低至1.2V),宽禁带半导体GaN,SiC的发展(各极间寄生电容显著减小),开关速度变快,在门极浮动的情况下,功率管将更容易被耦合误开。即使外部GS间加入10k的下拉电阻,由于其放电时间常数大,并不能有效的将耦合电压VGS下拉。

因此,在设计芯片时,需要考虑各种工作状态下,功率开关管是否存在栅极浮空状态。原边Flyback控制芯片在VDD电压较低时(小于2V),原边功率管是没有下拉能力。但由于此期间,VDS不存在高速变化的VDS,所以不存上述风险,但副边同步整流SR就会存在该风险。

在Flyback刚开始工作,即软启动阶段,副边控制同步整流功率管的芯片还未能供电或者供电不足,SR的MOS的门极处于高阻状态,在原边功率管快速开通时,SR容易耦合误开,形成原副边共通。原边Flyback IC可能触发SCP保护,如果保护未及时地触发,副边回路由于有很大的反向电流,SR MOS的VDS会出现较高的电压尖峰,甚至烧毁。因此SR控制芯片的内部要快速建立对外部功率管的下拉功能,这样避免原边管快速开通时,功率管烧毁。

除了芯片在未供电前,功率管会出现浮空状态;在芯片状态切换,如VDD达到开启阈值或者退出休眠模式,芯片使能驱动模块会需要一定的时间,在这段时间内,驱动输出较容易呈高阻。所以在设计IC时,应给驱动模块留有足够的使能时间,避免该期间高速变化的VDS使功率管栅极耦合误开。