MOS管工作区间及开通过程分析

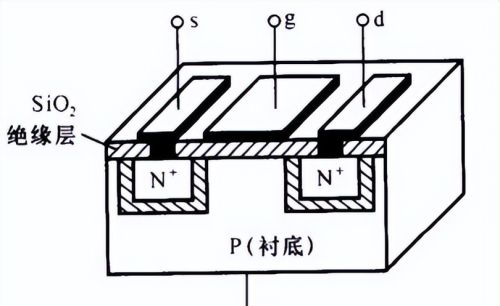

N沟道增强型MOS管的结构如图1所示,P型衬底上制作两个高掺杂的N区,引出作为漏极D和源极S,衬底上再制作一块绝缘层,绝缘层上在制作一层金属电极,引出作为栅极G,即构成了常见的N沟道增强型MOS管。一般而言,衬底B和S极会连在一起,当在栅极处加正电压时,靠近衬底的绝缘层会产生感应电荷,当感应电荷足够多时,D和S之间形成导电沟道,只要DS之间有电压,即可产生电流。另外,从结构上看,衬底B和S以及D之间都有一个PN结,但是B和S连在一起,所以BS之间的PN结被短路,B(S)和D之间的PN结即是的MOS的寄生二极管。(本文参考的模电书为《模拟电子技术基础(第四版)》,高等教育出版社,童诗白,华成英主编)

图1 N沟道增强型MOS管的结构示意图

1. MOS管工作区的划分

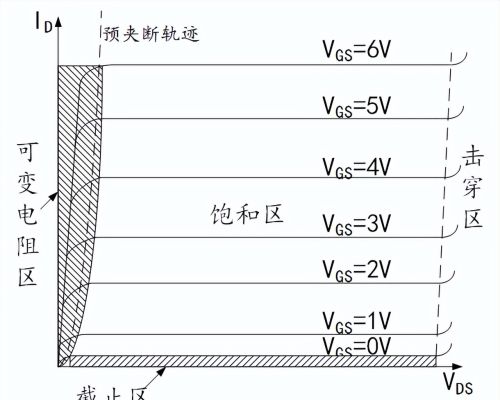

图2 MOS管输出特性曲线

首先介绍一下模电书上对各工作区的介绍:

夹断区:当VGS<Vth时,MOS管导电沟道被夹断不导通,此时ID≈0。

恒流区(饱和区):当VDS>VGS-Vth(即VGD<Vth)时,MOS管进入恒流区,在此工作区内,VDS增大时,ID仅略微增大,因此可将ID看作是受VGS控制的电流源,当MOS管做放大管使用时,工作在此区域

可变电阻区:当VDS<VGS-Vth(即VGD>Vth)时,MOS工作在可变电阻区,在此区域中,可通过改变VGS的大小来改变MOS的导通电阻大小

关于MOS管的夹断:当VGS为一固定值时,若在DS之间加一正向电压,则必将产生漏极电流,并且VDS的增大会使ID增大,沟道沿源漏方向变窄,并在VDS=VGS-Vth(即VGD=Vth)时,出现预夹断,随着VDS继续增大,MOS将承担管子的压降,但漏极电流基本不变,管子进入恒流区。

以上便是教材中对MOS工作区极夹断现象的描述,由此,可以自然而然地提出以下问题:

1).夹断区和MOS管的夹断是一回事吗?

实际不是,因为当驱动电压小于MOS的导通门限时,MOS管是没有形成导电沟道的。而书中对MOS管的夹断也明确写出MOS管出现夹断现象时,管子工作在恒流区。为更好地区分这两种工作状态,在图2中,我把这一区域称为截止区。

2).为什么预夹断电压是VDS=VGS-Vth(即VGD=Vth)?

因为Vth是MOS管的导通电压,这意味着在这个电压下,导电沟道刚刚形成。当漏极电压升高到VGD=Vth时,说明导电沟道靠漏极一端的电压降到了导通电压,所以MOS管漏极出现夹断。

3).夹断时,MOS管为什么由电流通过?最大漏极电流为什么由VGS确定?

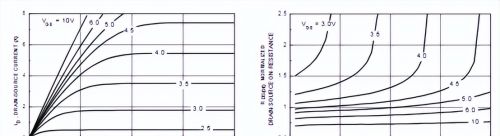

当VDS大到一定程度,MOS管被完全夹断,这其实是反型层的载流子在电场作用下迅速流动的变现而非导电沟道消失。并且,VGS大小决定了反型层的厚度,即决定了载流子的多少。在这种情况下,VDS的越增加,导电沟道的夹断区越长,电阻越大,VDS主要用于克服导电沟道夹断导致的电阻的上升对电流的影响,而VGS的增加则可拓宽导电沟道,所以此时的最大漏极电流由VGS确定。图3摘录了NDS351N 的数据手册,可以看到,VGS一定时,导通电阻随ID越增加而增加,这导致了VDS的上升,VGS越小,这一现象越明显(越容易夹断)。

图3 MOS管器件手册中ID-VDS和Ron-ID关系

总的来说,MOS做开关管使用时,其工作状态在截止区和可变电阻区之间切换,做放大管使用时,工作在饱和区。现如今,大部分的文档对MOS的工作状态的描述都是假设VGS不变,让VDS增加,描述这一过程中MOS管工作状态的变化。但当我重新回头看这么一段描述,浮上我脑海中的最大疑问是:为什么VDS会增加?这是因为在实际的应用场景中,VDS是基本固定不变的,被操纵的一般是驱动电压VGS。而且在作者的工作中,接触的都是工作在开关状态下的MOS,其导通压降很小,很难想象VDS逐步增大的场景,所以下文将从VDS固定不变,VGS压逐渐变大的角度分析MOS的开通过程。

2. MOS管的开通过程

关于MOS管的开通过程,网络上有许多文档进行分析,其来源应为一篇带感性负载的MOS管开通过程的分析,很多转发该文章的网文却常常忽略了这一点,把这个过程当做了所有场景下MOS的开通过程。因此,在分析之前,先说明本文分析的前提:阻性负载下,VDS固定时,加驱动电压VGS的情况下,MOS管的导通过程分析。

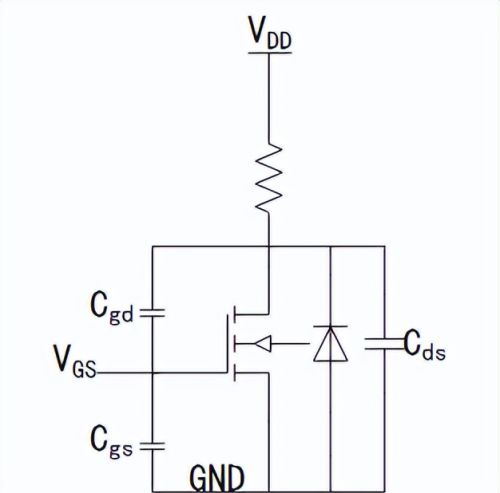

图4 带阻性负载的MOS管电路

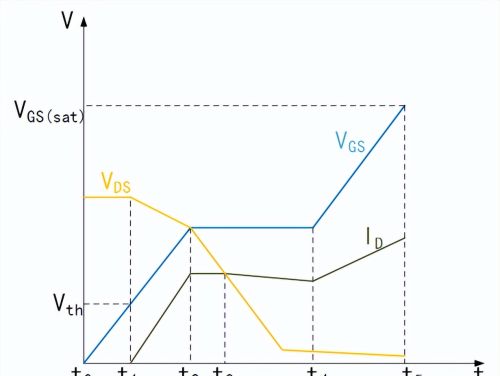

带阻性负载的MOS管电路模型如图4所示,其在GS、GD、DS之间都有寄生电容,在DS之间还有一个寄生二极管。在t0时刻,MOS管栅极加驱动电压VGS,其值为MOS管完全导通所需要的驱动电压VGS(sat),其开通过程中,VDS、VGS、ID的变化如图5所示。分析如下:

图5 MOS管开通过程

t0~t1:在此区间内,VGS给Cgs充电,但由于Cgs两端电压尚未上升到MOS管的阈值电压,所以MOS管处于截止状态。另外,由于VDD一直存在,所以Cgd的电压应该是从-VGD逐渐上升的(D极电压大于G极)。

t1~t2:t1时刻,Cgs两端电压大于MOS的导通压,此时MOS管开始导通,漏极电流形成,Cgd通过MOS管开始放电,VDS也开始下降。这段时间里,VGD<0<Vth,

MOS管处于夹断状态,工作在饱和区。

t2~t3:t2时刻,VDS两端电压下降到与VGS一致,此时VGD=0,MOS管进入密勒平台,栅极电流开始给Cgd充电,由于VGD开始上升,靠近漏极一侧的导电沟道逐渐变宽,MOS管夹断现象开始消失,导电沟道的扩宽使得VDS迅速下降。到t3时刻,VGD=Vth,MOS管的VGD上升到预夹断电压上,此阶段,MOS管依然工作在饱和区,而在密勒平台,VGS基本不变,因此,ID无变化。

t3~t4:t3时刻后,由于VGD>Vth,MOS管进入可变电阻区,在密勒平台的持续时间里,VDS的压降会降至基本等于饱和导通压降(否则栅极电流应该还是大部分会给Cgd充电,Cgs电压不会抬高),此时VGS不变,VDS下降,MOS管工作在可变电阻区,那么按照MOS管的工作特性曲线,ID应略有下降。

t4~t5:t4时刻,MOS管的密勒平台结束,Cgs继续充电至VGS(sat),ID随着VGS的增大而增大(导电沟道扩宽使导通电阻变小,ID上升,前提是负载足够重),此时MOS管饱和导通,工作在可变电阻区。

后续,若负载继续加重,使漏极电流继续上升,则MOS管的电流将会饱和,MOS管进入饱和区。