阻容感基础:电阻器应用

一,电阻器应用

很显然电阻器是硬件设计中最基本的元器件之一,它在硬件设计上的应用非常多样:可以单独应用于电路,也可以像变形金刚一样,同其它器件组成复杂电路。但是电阻器的应用无论怎么变化,我们都可以基于电阻器的本质:“电阻”进行原理分析。那么在电路中“电阻”能够用来做什么呢?

1. 在相同电压下,使用不同阻值的电阻器可以得到不同的电流:I = U/R;

2. 在相同电流下,使用不同阻值的电阻器可以得到不同的电压:U = I*R。

我们根据U=I*R公式可以看到:在实际应用中电阻器必须通过其电压降或电流大小,才能体现其作用,而“电阻”特性本身并不能参与信息处理、传输、存储(因为我们并不能直接观测到“电阻”)。所以对于电阻器的应用来说,我们需要得到不同电阻器带来的电压或电流变化,实现电路中所需电压或电流的设计目的。

对于特殊用途电阻器,举个例子:压敏电阻器(PTC,NTC),热敏电阻器、光敏电阻器等等,它们的电阻值变化机制以及应用场景相对比较明确,我们能做的是:严格按照器件规格资料中参数和应用条件,进行选择和电路设计。

然而普通电阻器正是因为其电阻特性的相对稳定,反而有更多样的应用设计,如下列举了其中一小部分简单的电阻器应用:

1. 保持信号状态稳定:上/下拉应用;

2. 限制线路电流大小:限流应用;

3. 调整线路信号质量(例如:匹配特征阻抗):线路匹配应用;

4. 电源电路中监测功耗:电流监测应用。

1,上拉/下拉应用

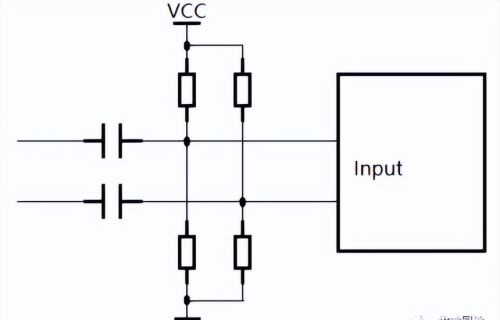

上拉/下拉:是将不确定的信号通过一个电阻器钳位在高/低电平,电阻器同时起限流作用;上/下拉电阻器的基本原理是:提供被上下拉的电路一定的电流驱动能力。

1. 上拉是对电路注入电流,即拉电流;

2. 下拉是对电路输出电流,即灌电流。

电阻器的上拉/下拉应用非常广泛,在不同硬件电路设计中,其作用也有所不同:

1. 保证器件输入管脚状态的稳定:

1, 边沿触发的输入管脚,如果器件内部没有内置上/下拉电阻,需外接上/下拉电阻器,使维持管脚不被误触发;

——例如中断、复位等可能为边沿触发的重要信号,必须保证其在工作期间的状态稳定。

2, 有些应用场合不希望出现高阻状态,可以通过上拉/下拉电阻器的方式使处于稳定状态;

——一些器件在上/下电瞬间的输出不受控(高阻),为保证输入器件管脚的稳定,外接上/下拉保证其正确状态;例如输入MOS管G极的信号,如果是高阻状态,则G极电荷积聚可能导致MOS管误导通。

3, 确保端口常态时有确定电平,例如:检测低电平的输入管脚,接上拉电阻器,使其常态就为高电平(适用一般设计原则);

——端口上/下拉的默认状态是否为管脚触发状态,取决于其应用需求,例如:单板上某个器件的启动有特定要求,初始默认要一直处于复位状态(假设低电平复位),那么其复位信号需下拉。

4, 解决总线驱动能力不足:上拉电阻提升管脚输出拉电流,下拉电阻提升管脚输出灌电流大小;

——例如,有些单片机的高电平驱动能力不足(一般器件管脚的低电平驱动电流大于高电平驱动电流),需要增加上拉电阻。

5, 悬空输入管脚比较容易受外界的电磁干扰(天线), 外部上/下拉可以提高总线的抗电磁干扰能力(关于电磁干扰相关的知识,后续《电磁兼容性基础》专题中分享)。

2. 用于输出/输出信号电平的转换或匹配:

1, 电平匹配:输出、输入信号不同电平之间的转换;

——1,TTL电平输出驱动CMOS电平管脚,由于高电平电压判断不同,需要上拉电阻器用于提升驱动电压;2,不同差分电平(LVPEC,HSTL等)的共模电压有差别,采用AC耦合后再输入端电阻上/下拉分压得到满足输入共模电压要求的电平。

2, 用于传输线终端匹配(例:戴维南匹配),具体原理后续“信号完整性”专题讲解。

3. 用于对CMOS结构器件输入管脚的保护:

1, 保护CMOS结构输入管脚内的保护二极管,防止保护二极管过流损坏;

——有些器件输入管脚内置保护二极管,防止输入信号电压超出管脚允许电压范围后破坏输入管脚内部结构,上下拉电阻有一定的分流能力,利于信号电平的稳定。

2, COMS结构输入管脚中不用的管脚不能悬空,一般接上/下拉电阻降低输入阻抗,提供泄荷通道,防止静电造成损坏。

——由于CMOS结构管脚的输入阻抗非常大,积聚在管脚上的电荷不容易泄放,容易损坏输入管脚。

4. 上拉电阻为OD/OC门提供驱动电流:

1, 根据IIC总线协议,上拉电阻的取值和I2C总线的频率及负载电容有关,电阻的大小对时序有一定影响,对信号的上升时间和下降时间也有影响;

2, 电阻计算公式:Rmin={Vdd(min)-0.4V}/3mA;Rmax = (T/0.874) *C。

2,上下拉电阻取值原则

在不同硬件电路设计应用中,对上拉/下拉电阻阻值的选择有不同考虑,整体来说有如下三个方面原则:

1. 从节约功耗及芯片的灌电流能力考虑:电阻值应当足够大;

——电阻大,电流小,损耗小。

2. 从确保足够的驱动电流考虑应:电阻值当足够小;

——电阻小,电流大,驱动能力大。

3. 过大的上拉电阻阻值,可能会使边沿变平缓(例如OD/OC门,靠上拉提供驱动电流)。

综合考虑以上三点原则,一般在数字电路的上/下拉电阻设计中选取:1k到10k之间。但电阻器的参数不能一概而定,要看电路其他参数而定:

举个例子:对于驱动TTL集成电路:上拉电阻的阻值要用1~10K之间;对于CMOS集成电路:上拉电阻阻值就可以选择相对较大(小于100K)。

3,限流应用

限流在某种意义上来说也是上/下拉应用中的一种,但是限流设计的目的更加偏重于对电路中电流的限制:电阻器在电路中限制电流的流过,电阻值越大电流越小。

——从欧姆定律I=U/R可知,当电压U一定时,流过电阻器的电流I与其阻值R成反比。

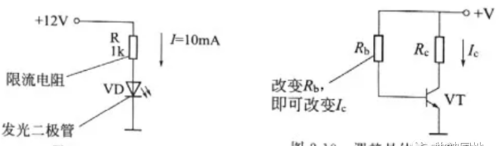

1. LED点灯电路:电阻器用于限制发光二极管的电流,控制发光量;

——LED通常最大电流在20mA~25mA左右,压降为2V左右,根据亮度需求,电流范围一般在5mA~15mA之间;但是不同应用场景(板内和对外接口,室内和室外等)的LED亮度要求不同,具体场景具体分析。

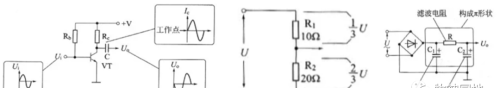

2. 三极管/MOS管电路,电阻用于控制三极管/MOS管所处的工作状态。

——根据三极管放大倍数,计算IBE电流和ICE电流关系,让三极管工作在预想工作区域:放大区或饱和区;在数字电路中MOS管一般当作理想开关(除缓启动等特殊应用),使其工作于可变电阻区。

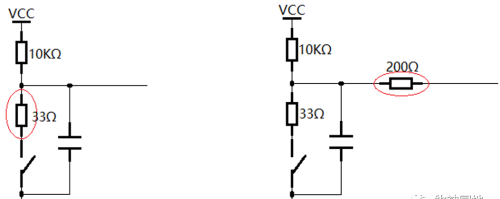

3. 按键、开关电路:串接电阻器用于限制电容器短路瞬间时的大电流冲击,避免电容器损坏和产生过冲脉冲;

——不止是按键/开关电路,类似有电容器电压瞬间接地的应用,都要考虑串接限流电阻,例如在位信号。

4. ESD防护电路:人容易触碰到的板内器件,可插拔连接器(单端信号线),面板接口(复位按键,指示灯等)等,这些位置更容易由接触而引入ESD,导致器件损坏,串接大电阻(百欧姆级别)用于ESD防护;

——对外通信/业务/调试接口或者重要的板内芯片调测试接口,使用专用TVS管来防护;另外,使用大电阻串接防护会对信号质量(边沿)有影响,高速信号需谨慎使用。

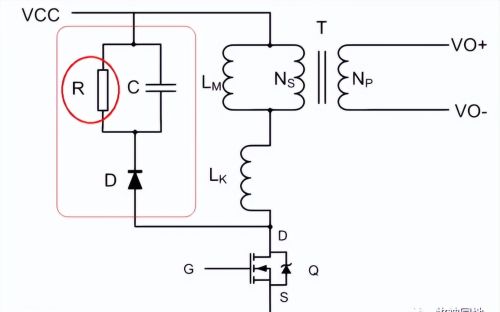

5. 开关电源脉冲尖峰吸收电路(RCD):MOS管开关瞬间存在电压尖峰,RCD电路用来吸收漏感能量,减缓电压尖峰。

——变压器原边电感存在漏感(Lk),MOS管关断瞬间漏感电流不能突变,导致MOS管D极电压产生尖峰,可能损坏MOS管。

4,0Ω电阻器应用

当年第一次看到0Ω电阻器,就突然懵逼了一下,觉得这是啥玩意?0Ω就是没有电阻值,那我要用这货有何用?事实证明了我当年的浅薄,因为后来有一段时间我用的最顺手的就是0Ω电阻器,而现在回过头来看,又证明了我那段时间的硬件设计水平的确不高。所以对于0Ω电阻器,我们的目标是:会用而又不滥用。有个问题是:在高速差分信号(大于1GHz)设计中,串接0ohm电阻器和100nF电容器(都是0402封装),大家觉得哪个对信号质量的影响更小呢?

1. 模拟地与数字地单点接地:如果将模拟地和数字地大面积直接相连,会导致数模之间的互相干扰;单点接地有很多种方式:阻、容、感(包括磁珠),单过孔,金属化机械孔等等,它们有不同的优缺点,根据实际需求进行设计;

——只要是地,最终都要接到一起后参考大地(大地是0电势等势体,无论在地球的哪个位置,其电势都为0);所以如果有地不接在一起会变成“浮地”,相互之间就存在压差,从而容易积累电荷产生静电(通过变压器的隔离地)。我们看到有些设备没要求接大地,但电网系统最终还是会接入大地,所以单板的电源最终还是会返回大地(单板内部电源也可能通过变压器回流了)。那地球为什么是等势体呢?其实地球的地壳并非良好的导体,我们脚下的大地同“漂亮国”大地之间的阻抗并非是0Ω。不过同学们可以将“大地”想象成大海,将“电流回流”想象成江水;并思考下:我们江河里的水流入大海后,我们这边和太平洋另一端的海平面就会明显不一样了么?

1, 磁珠连接:带阻限波器,抑制某一频段(高频段)的噪声,预先评估噪声频点,并选择合适磁珠;

2, 电容连接:隔直通交流,没有直流通路,会累计电荷造成浮地;

3, 电感连接:抑制低频段噪声干扰;

4, 0Ω连接:相当于很窄的电流通路(类似单点接地),能够有效地限制环路电流,使噪声得到抑制。

2. 为调试方便或电路兼容设计需求;

——在硬件设计过程中总会碰到一些不明确的设计需求,或者无法确定实际电路效果,所以需要设计0Ω电阻提供一个试错后的调整机会。

1, 作跳线使用;例如:IIC控制器二选一电路;

2, 匹配电路中参数不确定,用0Ω替代,调试后再替换;

3, PCB布线时走线困难,用0Ω跳过;

4, 方便调测试;

——利用0Ω电阻器建立方便调试的硬件通道,在正式版本中取消;利用0Ω电阻可以接电流表,方便电流测试;

5, 用于电流回路平面不连续时的跨接:当分割电源/地平面后造成信号最短回流路径的断裂,在分割区上跨接0Ω电阻器(不同电位平面之间使用nF级别电容),可以提供更短的回流路径;

6, 替代跳线座/拨码开关:使用选焊确定不同单板/应用场景的不同配置,避免拨码开关/跳线帽的失效风险。

5,其它应用

1. 降压应用:电流经过电阻器时必然会产生电压降,电阻值越大,电压降越大(U=I*R);

1, 放大器的负载电阻:应用了电阻器的降压作用(如下图左);

——三极管并不能放大能量,而是通过放大Ic电流(Ic = Ib*β)大小而产生不同的压降,实现达到信号放大的目的,所以电阻器在三极管放大电路中是降压作用。

2, 电阻器R1和R2构成一个分压器:经过这两个电阻的电流I相等,所以R1上压降为U,R2上压降为U,分压比为R1/R2(如下图中);

——电阻分压电路非常常用,例如开关/LDO电源电源电压检测反馈电路;电源电压监控电路(分压到特定值),电平匹配电路等等,选择合适的分压电阻精度和阻值是关键。

3, RC滤波网络:一种特殊的分压器(如下图右)。

——RC整流滤波电路中R与C2可理解为分压器:输出电压Uo取自C2上的压降;C2的直流容抗无限大,交流容抗随信号频率的增加而减小,因而C2上直流压降很大,而交流压降很小,达到低频滤波目的。

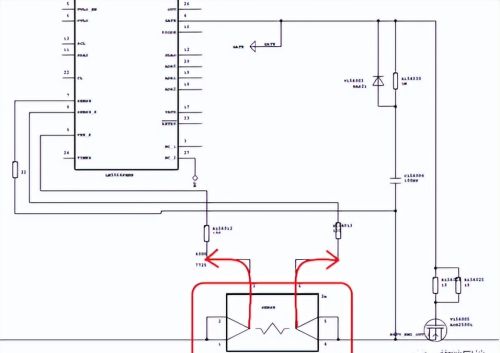

2. 电源电流监测应用:采用精密大功率电阻(例如:金属箔电阻器)串接在电源电路上,缓启动芯片监测电阻两端电压,从而监控电源功率;

——首先需选择监测电阻阻值小(mΩ级别)、精度高、功率大(几W),所以一般薄膜和厚膜电阻器并不适用;其次电阻焊盘上不同位置的电流分布不同,与采样电阻的布局布线关系很大,监测点选择电阻焊盘中心比较合适。

3. 提供负载电路:一些开关电源/LDO有最小工作负载的要求,此时在电源输出端增加并接电阻,用于提升电源模块工作的稳定性;

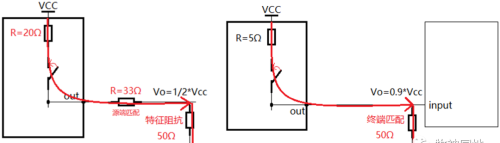

4. 传输线阻抗匹配应用:传输线阻抗匹配电阻是一种非常普遍的应用;一般分为:源端串联匹配和终端并联匹配两种,示意图如下所示。

二,电阻器的失效

电阻器的失效有各种不同原因,同时也有多种不同的失效表现;我们首先需要区分清楚的是:电阻器器件本身失效与电路失效是两个不同的概念。例如,上拉电阻由1KΩ(1%精度)变成10KΩ,对于电阻器本身来说已失效,但对于所应用的电路来说则不一定失效。下面我们将讨论电阻器器件本身失效机制。

——失效模式:各种失效的现象及其表现的形式;失效机理:导致失效的物理、化学、热力学或其它过程。

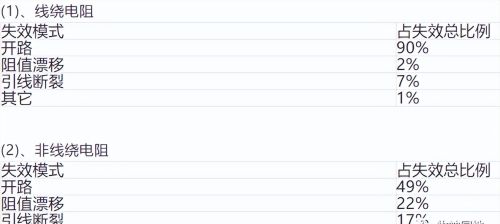

1. 开路(主要失效):主要失效机理为电阻膜烧毁或大面积脱落(电应力),基体断裂、引线帽与电阻体脱落(机械应力);

2. 阻值漂移超规范(次要失效):电阻膜有缺陷或退化,基体有可动钠离子,保护涂层不良;

3. 引线断裂:电阻体焊接工艺缺陷,焊点污染,引线机械应力损伤;

4. 短路:银的迁移,电晕放电。

那电阻器详细失效机理是什么呢?我们可通过了解其失效机理,从而提升硬件电路的可靠性设计:

1. 导电材料的结构变化;

1, 电荷高温老化:电负荷在任何情况下都会加速电阻器的老化进程,电阻体与引线帽接触部分的温升超过了电阻体的平均温升(电荷老化比温升老化影响更大),通常温度每升高10℃,寿命缩短一半;

——如果过负荷使电阻器温升超过额定负荷时温升50℃,则电阻器的寿命仅为正常情况下寿命的1/32。

2, 直流负荷:电解作用:直流负荷作用下,电解作用导致电阻器老化;在潮热环境下,电解过程更为剧烈。

——电解发生在刻槽电阻器槽内,电阻基体所含的碱金属离子在槽间电场中位移,产生离子电流:如果电阻膜是碳膜或金属膜,主要是电解氧化;如果电阻膜是金属氧化膜,则主要是电解还原。对于高阻薄膜电阻器,电解作用的后果可使阻值增大,沿槽螺旋的一侧可能出现薄膜破坏现象。

2. 硫化:在含硫环境中,贴片电阻阻值变大甚至变成开路。

3. 气体吸附与解吸;

1, 膜式电阻器的电阻膜,在晶粒边界或导电颗粒和黏结剂部分可能吸附非常少量的气体,构成了晶粒之间的中间层,阻碍了导电颗粒之间的接触,从而明显影响阻值;

——由于气体吸附与解吸发生在电阻体的表面,所以对膜式电阻器的影响较为显著,阻值变化可达1%~2%。

2, 温度和气压是影响气体吸附与解吸的主要环境因素,对于物理吸附:降温可增加平衡吸附量,升温则反之。

4. 氧化:氧化是长期起作用的因素(与吸附不同),氧化过程是由电阻体表面开始,逐步向内部深入;除了贵金属与合金薄膜电阻外,其他材料的电阻体均会受到空气中氧的影响,氧化的结果是阻值增大。

——防止氧化的根本措施是密封(金属、陶瓷、玻璃等无机材料),采用有机材料(塑料、树脂等)涂覆或灌封,不能完全防止保护层透湿或透气,虽能起到延缓氧化或吸附气体的作用,但也会带来与有机保护层有关新的老化因素。

5. 有机保护层的影响:有机保护层形成过程中,放出缩聚作用的挥发物或溶剂蒸气,热处理过程使部分挥发物扩散到电阻体中,引起阻值上升;其显著影响阻值的时间约为设备加工(热处理)后的2~8个月。

6. 机械损伤:电阻的可靠性在很大程度上取决于电阻器的机械性能。

——电阻体、引线帽和引出线等均应具有足够的机械强度,基体缺陷、引线帽损坏或引线断裂均可导致电阻器失效。