PDN的组成

1,电源模块(VRM)

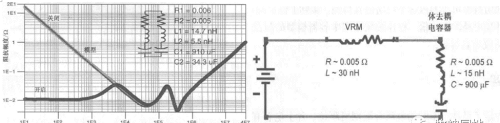

电源模块决定了电源分配网络的低频阻抗,所有的电源模块都会有一个输出阻抗曲线,如左下图所示,电源模块起作用的频段在0~4KHz左右;在4KHz以后的电源分配网络阻抗曲线与双电容模型一致。我们将电源分配网络按频率区域划分成3部分:

1 在< 1KHz时:若电源模块开启,输出阻抗会下降几个数量级,输出电压保持恒定,与其电流负载无关;

2 在1KHz到4KHz时:阻抗不断增加,4KHz时阻抗与电容其的阻抗相匹配;

3 在 > 4KHz时:电源分配网络阻抗完全由无源电容所决定,电源模块不起作用。

所以所需滤波电容(电解电容)的总容量,可以通过电压模块不能维持低阻抗频率处(1KHz)的目标阻抗去估算:Cbulk > 1/(Ztarget*2π*1KHz) = 160uF/Ztarget。

在实际应用中,开关电源的输出阻抗模型很难获得,我们假设开关电源设计合理稳定(通过电源动态响应、环路稳定性、纹波电压等测试),保证在低频段区域满足电源响应的要求。

1,去耦电容

在<100KHz低频段时有电源模块(VRM)、滤波电容为单板电源分配网络提供低阻抗;但在> 100KHz频段就需要板载去耦电容(陶瓷去耦电容和电源/地平面电容)为电源分配网络提供低阻抗。

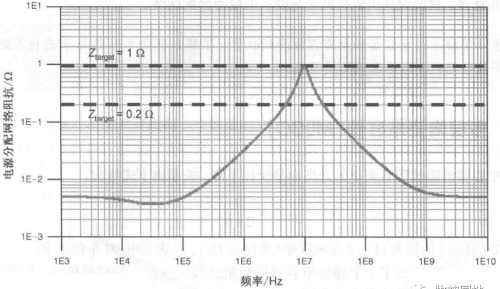

如下图为未加其它去耦电容器,只包括电源模块、滤波电容和50nF片上电容的电源分配网络阻抗;如果目标阻抗是1ohm,那么即使未加其它去耦电容器,也能满足电源分配网络设计要求,即使目标阻抗为0.2ohm,只要电流频谱幅度峰值在5~20MHz频率范围内没有出现尖峰,单板也能正常工作;此时无论板级电源分配网络如何设计,单板都能正常工作;会让人产生一种错觉:去耦电容并不那么重要!这是对去耦电容很大的误解,并不是所有的单板能够这么幸运。

21去耦电容模型

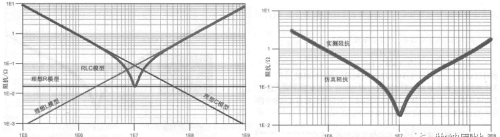

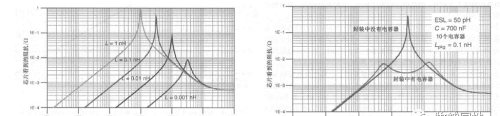

理想电容器的阻抗随频率升高呈反比下降:Z=1/2πƒC,但是实际电容还有寄生电感和电阻,其行为不像理想电容;如下图所示,我们在《电容器》专题已经分析了:在有寄生电感和电阻的模型中,电阻、电感和电容都是理想元件,它们的参数随频率恒定不变(<1GHz),其阻抗曲线非常接近实际电容器的实测阻抗,在不同的频段呈现出不同的特性:

1 低频时:自谐振频率以下,RLC电路阻抗取决于理想电容,电容呈现的是容性;

2 高频时:自谐振频率以上,RLC电路阻抗取决于理想电感,电容呈现的是感性;

3 自谐振频率点:理想电阻(ESR)决定了RLC的最低阻抗,电容呈现的是阻性。

自谐振频率点计算:ƒSRF = 1/2π*1/ = 159MHz/。

22去耦电容的寄生电感(ESL)

寄生电感对电源分配网络非常重要,也是设计电源分配网络的原因(如果没有寄生电感,那么久不需要设计这么复杂的电源分配网络);电容器的寄生电感通常称为等效串联电感(ESL),ESL的值主要由电容器的安装方式决定:反映了安装方式的情况而不是电容本身。

——举个例子,如下图所示,X2Y的电容并不是电容本身ESL较低,而是由于其特别的设计使得安装电感更小;这种安装方式:减小了ESL,使得自谐振频率点抬升,而在高频段由于ESL的减小,使得电容表现出更小的阻抗,这种安装方式减小ESL的同时也会影响ESR。

2,平面电容

根据电容的定义,任何两块导体中间夹着一块绝缘体都构成了电容;而电源与地平面之间明显也存在这个电容;同时电源-地平面电容的引脚电感(ESL)为0、ESR为0,所以在非常高频率上可以减少电源和地的噪声。

——根据传输线理论中的平面电容计算方法,平面电容容值为:C = 0.225*εr*A/d;假设电源-地距离为10mil,介质为FR-4材料,那么平面电容大小约为:100pf/in²。

如下图所示,平面电容是板级电源分配网络所能起到作用的最高频段,在PCB设计中要充分利用电源-地平面电容,尽量减小间距以增大平面电容容值,对电源分配网络阻抗设计至关重要。

3,封装屏蔽

集成电路封装是指:芯片(Die)焊盘与单板器件焊盘之间部分,包括:焊盘、键合线等;在电源/地的芯片焊盘到单板焊盘之间串联了一个封装引脚回路电感,成为电源分配网络阻抗的一道屏障:ZL = 2πƒL;跨过这道屏蔽,我们就进入了芯片(Die)内部了。

不同封装的引脚电感相差很大:大到几十nH小至几十pH;除了封装引脚电感,还有连到单板的过孔回路电感,以及电源/地平面上运送电流过程中的扩散电感。

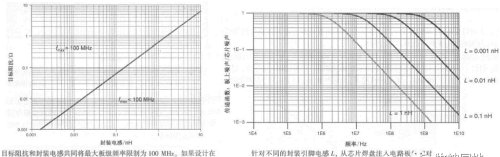

考虑封装电感和片上电容的相互作用,单板为短路阻抗时由芯片看向电源分配网络阻抗曲线,如下左图所示,该阻抗由封装电感决定:无论怎么设计板级电源分配网络,都不可能将芯片(die)看向电源的网络分配阻抗减小到比封装引脚阻抗更小;由于封装电感与片上电容相互作用,会出现很大并联谐振阻抗尖峰,如下右图所示,此时可以通过封装中的去耦电容抑制。

为了确定板级电源分配网络的设计目标,先确定由封装引脚、过孔和扩散电感共同组成的阻抗开始超过目标阻抗时的频点,这是板级阻抗对芯片发挥作用的高频上限频率;封装引脚电感、最高有效频率和目标阻抗之间的关系:Ztarget < 2π*Lpkg* ƒmax。

给出100MHz频率下,封装电感和目标阻抗的关系如左下图:如果单板目标阻抗在斜线下方,此时目标阻抗很低,封装引脚电感很大,那么单板最高有效频率低于100MHz;当封装中有去耦电容时,板级阻抗最高有效频率往往小于100MHz。

如右下图所示,封装电感大的另外一个好处是:它作为一个过滤器,以防止高频噪声从芯片的电源分配网络跑到单板上,封装引脚电感越高,板上电压噪声就越少。

4,片上电容

器件内部的滤波电容包括了:封装电容和片上电容;器件电容的作用已在上一节简单描述,而片上电容:决定了更高频段的电源分配网络阻抗。然而片上电容并不像封装电容,是一个个电容元器件,而是芯片内部的各种寄生电容:

1 芯片内部电源层和地层之间的电容;

2 所有P管/N管的栅极电容(栅极电容的具体分析,后续在《MOS管基础》专题详细讲解);

3 其它各种寄生电容。

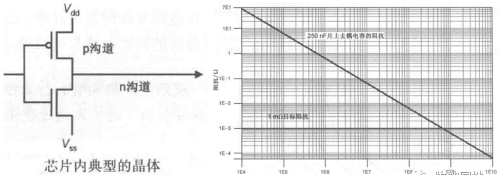

芯片上最大的电容源自分布在片上各处的栅极电容(面积大,数以百万计),在任何时刻PMOS和NMOS都是一个开启一个关闭;这意味着总有一个MOS管的栅极被连接到芯片的电源与地之间,由栅极形成的单位面积电容近似为:C/A=8.85* F/m² *DK/h。

——举个例子,对于130nm工艺芯片,P/N管的片上电容约为:C/A=130 nf/cm²;65nm芯片片上电容约为:C/A=260 nf/cm²。

如下右图为250nF片上电容的阻抗曲线图。