> 汽车交通

硬件基础——PN结

1. 本征半导体

本征半导体(Intrinsic Semiconductor):不含杂质的半导体成为本征半导体,主要有单晶硅和单晶锗。

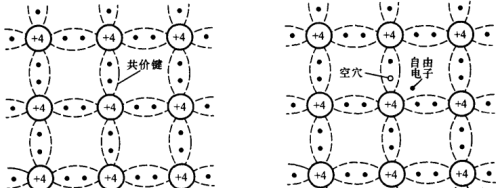

2. 自由电子与空穴

半导体硅和锗的最外层有四个电子,为处于稳定状态,每个原子的价电子都要和相邻原子的价电子配对,形成共价键。但共价键中的电子没有结合的那样紧密,由于能量激发,一些电子会成为自由电子。同时,某处共价键失去一个电子形成空穴。自由电子和空穴总是成对出现。

3. 本征半导体的导电性

在本征半导体两端加电压,自由电子向正向移动,形成电子电流;空穴向负极移动,形成空穴电流。但由于两种载流子数量很少,所以本征半导体的导电性很弱。

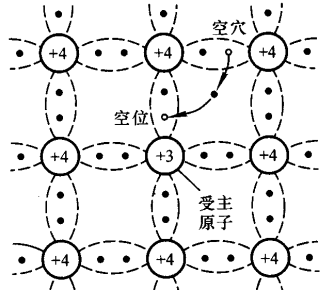

4. P型半导体和N型半导体

如果向本征半导体中掺入少量的杂质,半导体的导电性会大大提高。在单晶硅中掺入少量的五价磷或三价硼,就构成了N型半导体和P型半导体。以P型半导体为例,由于硼有3个价电子,和相邻硅原子形成共价键时,因缺少一个电子而多一个空穴,从而空穴变多形成P型半导体。

5. PN结的形成

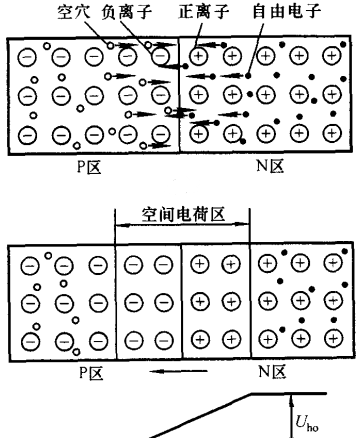

将一块本征半导体的两边掺入不同的元素,一边为P型,另一边位N型。由于两边的载流子浓度不同,会产生扩散现象。

在扩散的过程中,一边失去自由电子带正电,一边失去空穴带负电,这样在P区和N区的交界处形成了一个内电场。N结内电场的方向由N区指向P区。

在内电场的作用下,两边的电子和空穴会做漂移运动。过一段时间,扩散和漂移运动达到了平衡。最后在交界面形成了一定厚度的空间电荷区,即PN结。

6. PN结的导电性

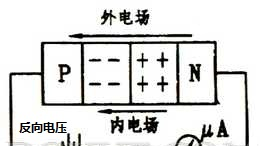

当加正向电压,扩散加剧,内电场被消耗,导通电流较大。

当加反向电压,漂移加剧,内电场被增强,导通电流较小。

因此,PN结具有单向导通性。