晶体和有源晶振的差异,你了解多少?

无源晶体即是咱们常说的谐振器,而有源晶振即是振动器,都是用来发生时钟信号的,但二者有很大差异。

一.晶体——crystal

无源晶体仅仅个石英晶体片,运用时需匹配相应的电容、电感、电阻等外围电路才干工作,精度比晶振要低,但它不需求电源供电,有起振电路即可起振,一般有两个引脚,报价较低。石英晶片之所以能作为振动器运用,是依据它的压电效应:在晶片的两个极上加一电场,会使晶体发生机械变形;在石英晶片上加上交变电压,晶体就会发生机械振动,一同机械变形振动又会发生交变电场,尽管这种交变电场的电压极端弱小,但其振动频率是非常安稳的。当外加交变电压的频率与晶片的固有频率(由晶片的尺度和形状决议)持平时,机械振动的起伏将急剧添加,这种景象称为“压电谐振”。

压电谐振状况的建立和保持都必须借助于振动器电路才干完成。一个串联型振动器,晶体管T1和T2构成的两级扩大器,石英晶体XT与电容C2构成LC电路。在这个电路中,石英晶体适当于一个电感,C2为可变电容器,调节其容量即可使电路进入谐振状况。该振动器供电电压为5V,输出波形为方波。

在电路运用中,由于晶体是有2个引脚的无极性元件,自身无法振动起来,因而需求借助于芯片内部的起振电路才干发生振动信号,在芯片的手册上有主张的衔接办法。无源晶体没有电压的疑问,信号电平是可变的,也即是说是依据起振电路来决议的,同样的晶体能够适用于多种电压,可用于多种不一同钟信号电压请求的CPU,并且报价一般也较低,因而关于一般的运用假如条件许可主张用晶体,这尤其适合于商品线丰厚批量大的生产者。无源晶体相关于晶振而言其缺点是信号质量较差,一般需求准确匹配外围电路(用于信号匹配的电容、电感、电阻等),更换不一样频率的晶体时周边装备电路需求做相应的调整。主张选用精度较高的石英晶体,尽也许不要选用精度低的陶瓷警觉。

二.有源晶体振动器——oscillator

在电子学上,一般将富含晶体管元件的电路称作“有源电路”(如有源音箱、有源滤波器等),而仅由阻容元件构成的电路称作“无源电路”。有源晶振内部除了石英晶体外,还有晶体管和匹配电容等外围电路,精度高、输出信号安稳,是一个完好的振动器,不需求规划外围电路、运用方便,但需求电源供电,有源晶振一般是四管脚封状,有电源、地线、振动输出和一个空置端。运用有源晶振时要特别注意,电源必须是稳压的且电源引线尽量短,并尽量与体系中运用晶振信号的芯片共地。

有源晶振不需求CPU的内部振动器,信号质量好,对比安稳,并且衔接方式相对简略(主要是做好电源滤波,一般运用一个电容和电感构成的PI型滤波网络,输出端用一个小阻值的电阻过滤信号即可),不需求杂乱的装备电路。有源晶振一般的用法:一脚悬空,二脚接地,三脚接输出,四脚接电压。相关于无源晶体,有源晶振的缺点是其信号电平是固定的,需求选择好适宜输出电平,灵活性较差,并且报价高。关于时序请求灵敏的运用,个人认为仍是有源的晶振好,由于能够选用对比精细的晶振,乃至是高级的温度抵偿晶振。有些CPU内部没有起振电路,只能运用有源的晶振,如TI的6000系列等。有源晶振对比于无源晶体一般体积较大,但如今很多有源晶振是表贴的,体积和晶体适当,有的乃至比很多晶体还要小。

几点注意事项:

1、需求倍频的DSP需求装备好PLL周边装备电路,主要是阻隔和滤波;

2、20MHz以下的晶体晶振基本上都是基频的器材,安稳度好,20MHz以上的大多是谐波的(如3次谐波、5次谐波等等),安稳度差,因而强烈主张运用低频的器材,毕竟倍频用的PLL电路需求的周边装备主要是电容、电阻、电感,其安稳度和报价方面远远好于晶体晶振器材;

3、时钟信号走线长度尽也许短,线宽尽也许大,与其它印制线距离尽也许大,紧靠器材规划布线,必要时能够走内层,以及用地线围住;

4、经过背板从外部引进时钟信号时有特别的规划请求,需求详细参考相关的材料。

此外还要做一些说明:

总体来说晶振的安稳度等方面好于晶体,尤其是精细测量等范畴,绝大多数用的都是高级的晶振,这么就能够把各种抵偿技能集成在一同,削减了规划的杂乱性。试想,假如选用晶体,然后自个规划波形整形、抗搅扰、温度抵偿,那样的话规划的杂乱性将是什么样的呢?咱们这儿规划射频电路等对时钟请求高的场合,即是选用高精度温补晶振的,工业级的要好几百元一个。

特别范畴的运用假如找不到适宜的晶振,也即是说规划的杂乱性超出了市场上制品晶振水平,就必须自个规划了,这种情况下就要选用晶体了,不过这些晶体必定不是市场上的一般晶体,而是特别的高端晶体,如红宝石晶体等等。

三.关于有源晶振的一些疑问:

1.请问有源晶振的最低频率是多少?

答1:理论上无限低。实际上我见过最低的是1MHz.更低的话加分频器即可。

答2:商品一般是M级,但能够经过分频器降频低于1M的商品有源晶振能买到的只需32768Hz的。

答3:有252kHz 的卧式晶振。

2.怎样用有源晶振?如今一般需求晶振的器材能够运用晶体加内部振动电路发生时钟或是直接运用有源晶振。此器材往往标明一个引脚XI 和XO。当运用晶体时,晶体的两头必定就连在这两个脚上。当运用有源晶振时是什么样呢?有源晶振输出应当接到哪一端呢?令一端应当怎样处理呢?(如同关于89系列单片机不一样工艺情况下处理是不一样的) 用XI,而XO悬空。

3.有源晶振输出串个电阻做啥用?

1)也许是信号完好性需求,减小过冲;

2)下降EMI;

3)5V晶振输出,3.3V器材输入,限制电流。

一般大公司硬件电路都有最小化规划,是长时间经验总结出来的,为的是削减重复性劳作和确保商品质量。咱们画图基本上直接抄模块电路,查看的人也依照标准电路查看,这么就不用每次都思考怎样规划。你说的晶振输出串电阻就来自于最小化规划,关于数字电路里最主要的时钟源有些,应当特别注意保证信号完好性,最小化规划中晶振外围电路除了电阻还要有一些别的器材。

串电阻是为了减小反射波,避免反射波叠加致使过冲。有时,不一样批次的板子特性不一样,留个电阻方位便于调整板子状况到最好。如无必要串电阻,就用0欧电阻衔接。反射波在大有些电路里有害,但PCI却恰恰利用了反射波构成有用信号。

(1) 削减谐波,有源晶体输出的是方波,这将致使谐波搅扰,尤其是阻抗严峻不匹配的情况下,加上电阻后,该电阻将与输入电容构成RC积分平滑电路,将方波转换为近似正弦波,尽管信号的完好性遭到必定影响,但由于该信号还要经往后级扩大、整形后才作为时钟信号,因而,功能并不受影响,该电阻的大小需求依据输入端的阻抗、输入等效电容,有源晶体的输出阻抗等要素选择。

(2) 阻抗匹配,减小回波搅扰及致使的信号过冲。咱们知道,只需阻抗不匹配,都会发生信号反射,即回波,有源晶体的输出阻抗一般都很低,一般在几百欧以下,而信号源的输入端在芯片内部结构上一般是运放的输入端,由芯片的内部电路与外部的无源石英晶体构成谐振电路(运用有源晶体后就不需求这个晶体了),这个运放的输出阻抗都在兆欧。

4.板子上面用到了一个56MHz的有源晶振但其辐射特别的严峻,如今晶振的电源管脚是直接接电源的,输出也是直接衔接的,我想是不是能够用磁珠和电容对电源管脚处理?请问各位老师谁供给一种详细的处理办法,包含所用器材详细的值!

1)屏蔽-用铜或铜镀银屏蔽;

2)接地-加宽地线下降地线电感;

3)电源滤波。

56MHz的有源晶振辐射严峻应怎样处理的疑问?请断定你的商品辐射源是经过有源晶振的自身仍是导线或是PCB铜皮走线,假如断定了源头, 你可经过加屏蔽,加电感电容或有用的接地等来改进,应当是能够的。

我觉得你不能断语即是由于晶振的辐射致使的搅扰,假如断定是辐射致使的搅扰,能够加金属的屏蔽,让晶振的外壳接地。假如并不是辐射致使的,那就要进一步做好电源的滤波,象你说的,还能够在被搅扰的电路和你的晶振的供电加一个磁珠。我个人认为,也许不是电源的滤波致使的,由于晶振的辐射的功率并没有那么大。仅仅我自个的观点。我本来看有人作规划的时候,把晶振做到电路外面,然后经过同轴线衔接进来,然后各自用屏蔽盒来阻隔,当然这是对比严苛军工项目,所以才那么费事。

四.晶振术语简释

一般最重视的参数有2个,即调整频差,负载电容。

Frequency Tolerance(调整频差):在规则条件下,在基准温度(25±2℃)与标称频率答应的偏差。一般用PPm(百万分之)表明。

Load Capacitance(负载电容):与晶体一同决议负载谐振频率fL的有用外界电容,一般用CL表明。

晶振技能参数详解

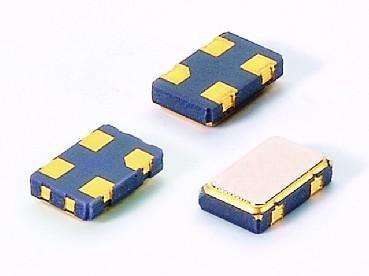

咱们一般会把石英晶体谐振器与石英晶体振动器统称为晶振。谐振器分为插件和贴片如49U,49S等,一般需求外接元件构成振动电路;振动器也可分为插件(DIP)和贴片(SMD),插件如长方形的DIP14封装,正方形的DIP8封装等,贴片有7*5,5*3.2等封装。

世界电工委员会(IEC)将石英晶体振动器分为4类:一般晶体振动(SPXO),电压控制式晶体振动器(VCXO),温度抵偿式晶体振动(TCXO),恒温控制式晶体振动(OCXO)。

1.一般晶体振动器(SPXO)可发生10^(-5)~10^(-4)量级的频率精度,标准频率 1—100MHZ,频率安稳度是±100ppm。SPXO没有选用任何温度频率抵偿办法,报价低廉,一般用作微处理器的时钟器材。封装尺度规模从21×14×6mm及5×3.2×1.5mm。