关于MOSFET驱动电路的设计

本文主要谈一谈MOSFET驱动电路的设计相关问题。

驱动MOSFET有隔离和直接耦合两种不同的电路形式。直接耦合的驱动电路主要应用在低压电路或非桥结构的MOSFET中,隔离式电路主要应用在高压、半桥和全桥形式的MOSFET电路。

下面首先介绍直接耦合的电路,直接耦合的电路由以下几个部分组成:充电回路、放电回路、限流电路、保护电路和加速电路。

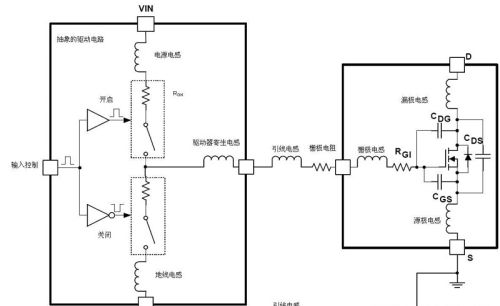

MOSFET驱动电路需要通过ROH对MOSFET栅极电容充电,通过ROL释放栅极电容上的电荷。抽象的直接耦合驱动电路可如图所示。

61.jpg1185x785 50.5 KB

我们可以发现,整个环路中存在这很多寄生的感抗的因素。这些寄生感抗包括驱动电路电源端电感、输出端电感、地线电感、驱动电路与MOSFET之间的引线电感、MOSFET的栅极、源极和漏极电感。 这些寄生电感是由MOSFET晶圆和封装之间的引线的感抗和源极封装引脚至MOSFET焊盘之间的感抗所组成的。

驱动器和MOSFET寄生等效模型

这些些寄生参数会影响驱动电路的性能,有些严重到影响整个电路设计。

① MOSFET的开启延迟和关断延迟增加:

由于存在栅极前面有多种寄生的电感的存在,使得MOSFET在开启和关断初期,驱动器的输出电流的变化率被大大限制了,输出电流的变化速度的减慢使得驱动器对栅极电容充电和放电的时间变长,整个开关过程被拉长了。在开启过程中,驱动电路电源电感、驱动器输出电感、引线电感和栅极电感起作用,反之在关断过程中地线电感和地线回路上的引线电感则会大大抑制关断的速度,这点直接导致了后面的加速电路的引入。

② 栅极前感抗和等效输入电容可能会发生谐振,在驱动电压的快速变化的时候,丰富的谐波频率给电感电容的串联提供足够的能量,其现象是在栅极发生震荡尖峰。因此不仅MOSFET内部存在栅极电阻RM,并在栅极前面还会加入RG,这两个电阻与驱动电路的内阻一起有效的消耗能量,抑制这个震荡。

由于MOSFET内部的电阻RM已经确定,因此只能通过选择栅极电阻和驱动电路内阻的方式进行电路的优化。电阻过小则会引起栅极电压的过冲且不能阻止振荡尖峰的存在,电阻过大则会使得开启过程变得过慢,加大了开启的时间。

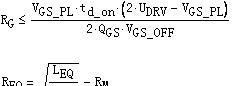

从谐振的角度考虑电阻选择为:

当然这个取值也要满足时间的需求,电阻也有一定的限制。

③ 源感抗会阻碍漏源极间电流IDS的变化。当MOSFET开启的时候,初始时电流变化率dI/dt偏大,因此在源感抗上产生了较大压降,从而使得源点电位抬 高,使得栅极电压分压在源电感上,使得栅极电容上的电压VGS减小,由于IDS变化较大,这个影响因素会很大程度上使得开关时间变长。

④ 在MOSFET开启状态的时候漏感抗起到了很好的作用,有效的限制了电流变化率,减少了开启的功耗。但是在关断的时候,漏源极间电压VDS形成明显的下冲,显著的增加了关断时候的功耗。

由于以上的一些因素,我们将考虑驱动电路的设计。由于驱动电路的功耗较大,主要分为几部分:栅极电容充电和放电产生的功耗、驱动电路交越穿通电流产生的功耗和静态电流产生的功耗。由于最后一部分相对较小,因此主要考虑前面两部分。

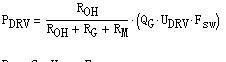

① MOSFET栅极电容充电和放电产生的功耗,与驱动器内阻ROH、栅极电阻RG、MOS栅极电阻RM、栅极电荷QG、驱动电压UDRV和开关频率FSW有关。

② MOSFET 驱动器交越导通穿通电流产生的功耗,与驱动管的交越常数CC、驱动电压UDRV和开关频率FSW有关。

计算公式如下:

大部分的集成芯片的输出电流都比较小,这是因为在控制频率较高的情况下,芯片的晶圆大小受到了一定的限制。在驱动器上较高的功耗很高也导致了IC的封装成 本较高,因此在驱动芯片往往只是提供较小的电流,由扩展电路完成对MOSFET的驱动,最为典型的是图腾柱结构,这是最便宜和有效地驱动方式,可采用三极管或者小功率MOS管实现。将输出电路贴近MOSFET以后,可使得暂态过程中的大电流环路尽可能小,配置专门的旁路电容以后,可很好的改善EMC特性, 降低地线引线电感和输出的引线电感。在三极管电路中,两个三极管的基极与源极之间的导通二极管有效的钳制住由引线电感引起的暂态浪涌电压。