单板EMC设计之时钟布局优化

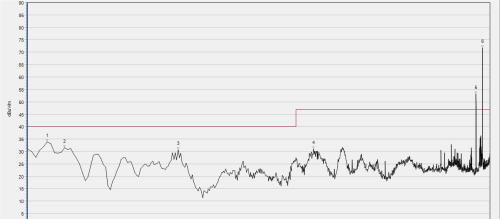

在进行整机RE辐射测试时,在频谱图上常会出现两种情形,一种是30M~300M的低频包络,另一种是300M~40G频段内的高频尖峰。前者一般是由电源或者接口电路驱动芯片激励线缆导致的辐射,后者一般是由时钟借助线缆或结构上的孔洞和缝隙对外进行泄露。本文主要讨论时钟导致的辐射情况,对于信号传输参考时钟导致的辐射只能通过滤波去加以抑制,如GE网口的4对差分线参考时钟为125M,测试时常会在频谱上发现125M及其倍频处的噪声尖峰,此时一般会通过网口变压器和去耦电容去加以抑制。对于时钟发生器本身或者其输出信号耦合到输出线缆上造成的辐射,一般可以通过优化时钟芯片布局加以解决,下面主要讲解如何优化时钟电路布局及走线来解决时钟辐射问题。

一|晶体电路应用及PCB设计

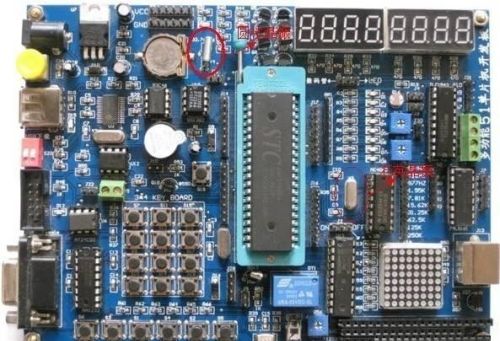

晶体一般应用在单片机小系统和计时芯片的电路中,为其提供电路运行必要的参考时钟,具体如下图所示。

∆单板上的晶体应用

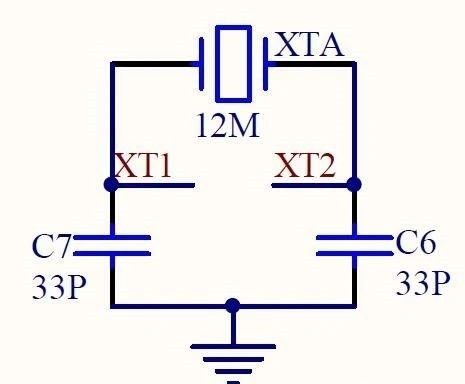

晶体电路一般比较简单,由晶体加2个电容组成,这两个电容分别为增益电容和相位电容。

∆晶体时钟电路

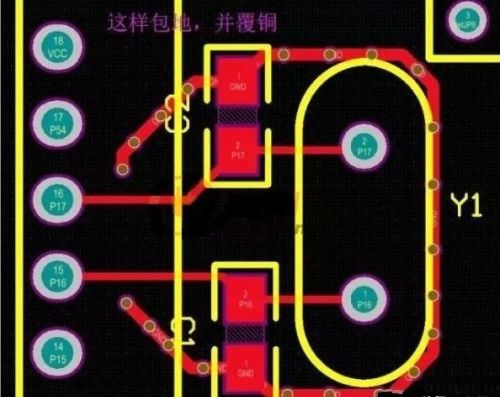

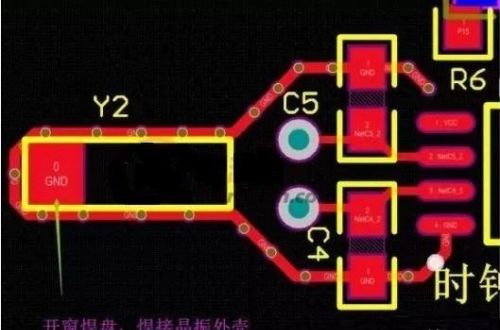

晶体电路的布局及走线如下图所示。

∆PTH封装晶体布局走线图

∆圆柱形晶体布局走线图

二|晶体电路布局走线注意事项

晶体电路布局注意事项:

(1)晶体电路和IC布在同一层面,这样可以少打孔;

(2)布局要紧凑,电容位于晶体和IC之间,且靠近晶体放置,使时钟线到IC尽量短;

(3)对于有测试点的情况,尽量避免stub或者是使stub尽量短;

(4)附近不要摆放大功率器件、如电源芯片、MOS管、电感等发热量大的器件,会影响晶体输出频率;

(5)晶体电路离板边及出面板信号500mil以上。

晶体电路布线应注意事项:

(1)和IC同层布局,同层走线,尽量少打孔,如果打孔,需要在附近加回流地孔;

(2)时钟走线采用类差分走线;

(3)走线要加粗,通常8~12mil,由于晶体时钟波形为正弦波,所以此处按模拟设计;

(4)信号线包地处理,且包地线或者铜皮要打屏蔽地孔;

(5)晶体电路模块区域相当于模拟区域,禁止其他信号穿过。