上电不规范,芯片就完蛋

为什么i.MX RT要好好讲讲上电呢?因为这里处理不好,往小了说系统不启动无法正常工作,往大了说,砰,烧掉了,所有工作都要重新来一遍。

在设计开发板,或者系统调试的时候,硬件工程师一定不能忽略一个重要的问题,就是芯片上电的先后顺序。如果我们使用i.MX RT时,无法满足上电时序的要求的话,可能会导致:

芯片启动阶段电流过大;

芯片无法正常启动;

最糟糕情况,对芯片造成不可逆的损坏。

如何避免以上情况产生呢?

最重要就是要注意i.MX RT上电时序。我们以i.MX RT1010为例,带领大家走一遍i.MX RT的上电过程。

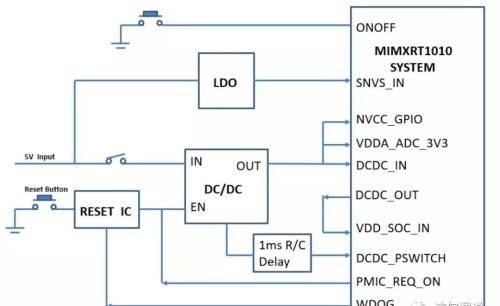

i.MXRT1010的外部电源电路图

i.MX RT1010的电源设计电路和上电时序图

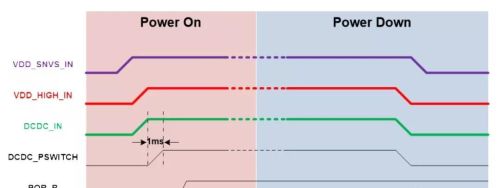

如上时序图中的VDD_SNVS_IN代表的是Supply input voltage to Secure Non-Volatile Storage and Real TimeClock;

VDD_HIGH_IN则是VDD_HIGH_INsupply voltage;

DCDC_IN则是Powerfor DCDC。

首先,第一个上电的是VDD_SNVS_IN。从时序图上,可以看到最上面就是VDD_SNVS_IN。其次,当VDD_SNVS_IN上电之后,i.MX RT1010芯片会输出一个驱动信号叫PMIC_REQ_ON,使能外部的DC/DC产生电能给DCDC_IN供电。这时VDD_HIGH_IN和DCDC_IN产生供电,起来工作了。在这种情况下,其实i.MX RT1010的外部供电就基本上已经完成了。

然后,i.MX RT1010的内核启动,还需要一个DC/DC。启动内核DC/DC需要在DCDC_IN供电之后,至少等待一个毫秒的时间。芯片内部会将DCDC_PSWITCH 这个信号拉高,内部的DCDC_OUT就会输出一个1.1V给VDD_SOD_IN。这样,i.MXRT1010所有的电压信号都就完成了。

最后,待所有的电源就完成了上电之后, POR_B的信号拉成高电平,告知芯片内部电源供电正常。

一句话总结上电时序:在VDD_SNVS_IN上电之后,VDD_HIGH-IN和DCDC_IN同时上电,再等一毫秒以后,DCDC_PSWITCH拉一个上升沿上去。

除上电时序外,上电不规范,内核也起不来

在上电的过程中,发现芯片无法工作的情况非常多。这里给大家举两个例子:

案例一:比如说挂上串口、挂上I2C、挂上JTAG,有时候我们DCDC 1.1V就出不来。这个问题的原因也是在PSWITCH这边。

在使用i.MX RT芯片时,很多的小伙伴们用的JLINK是非正常渠道的JLINK,内部会有一个自供电的功能。在插上芯片的一瞬间,自供电的功能很有可能早于SNVS这个电源域的上电,就会造成内部的电源域工作不正常。

所以如果大家有手头上有这种不正规的JLINK,一定要把自供电功能给它去掉,就可以了。

案例二:比如有一个pin脚上挂上一个3.3V的一个上拉电阻比SNVS上电早。这种情况下,很容易就造成i.MX RT1010内核的1.1V起不来。

总之,一定要保证SNVS上面不要有任何的外部的电源。