关于顺序逻辑电路设计的教程,快收藏起来吧

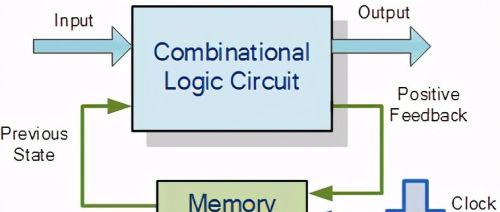

与当时根据输入的实际信号改变状态的组合逻辑电路不同,顺序逻辑电路具有某种形式的内置“存储器”。

这意味着顺序逻辑电路能够考虑其先前的输入状态以及实际存在的输入状态,因此顺序电路会涉及某种“之前”和“之后”效果。

换句话说,“顺序逻辑电路”的输出状态是以下三个状态的函数:“当前输入”,“过去输入”和/或“过去输出”。顺序逻辑电路会记住这些条件,并保持固定在其当前状态,直到下一个时钟信号改变一种状态为止,从而为顺序逻辑电路提供了“存储”。

顺序逻辑电路通常被称为两个状态或双稳态设备,可以将其输出或输出设置为两种基本状态之一,即逻辑电平“ 1”或逻辑电平“ 0”,并且将保持“锁存”状态(因此得名)在当前状态或条件下无限期地锁存),直到施加了一些其他输入触发脉冲或信号,这将导致双稳态再次改变其状态。

顺序逻辑表示

“顺序”一词是指事情以一种“顺序”发生,一个接一个地发生,在顺序逻辑电路中,实际的时钟信号决定了接下来什么时候发生。简单的时序逻辑电路可以由标准的双稳态电路构成,例如:触发器,锁存器和计数器,它们本身可以通过以特定组合方式将通用与非门和/或或非门简单地连接在一起以产生所需的时序电路而制成。

顺序逻辑的分类

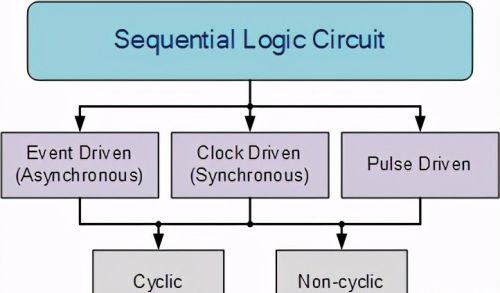

由于标准逻辑门是组合电路的组成部分,所以双稳态锁存器和触发器是顺序逻辑电路的基本组成部分。顺序逻辑电路可以构造为产生简单的边沿触发触发器,或者产生更复杂的顺序电路,例如存储寄存器,移位寄存器,存储设备或计数器。无论哪种方式,顺序逻辑电路都可以分为以下三个主要类别:

1.事件驱动 –启用后立即改变状态的异步电路。2.时钟驱动 –与特定时钟信号同步的同步电路。3.脉冲驱动 –这是对触发脉冲作出响应的两者的组合。

除了上述逻辑电平“ 1”和逻辑电平“ 0”所提到的两个逻辑状态之外,还引入了第三个元素,该元素将顺序逻辑电路与其组合逻辑对应物tiME分开。复位后,顺序逻辑电路将返回到其原始稳态,具有回路或反馈路径的顺序电路实际上被称为“循环”的。

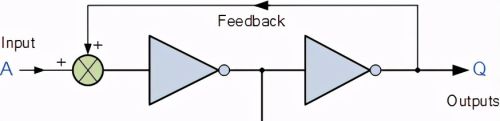

现在我们知道,在时序电路中,变化仅在时钟信号的施加下才发生,从而使其变为同步,否则电路是异步的,并且取决于外部输入。为了保持其当前状态,顺序电路依赖于反馈,当一部分输出反馈到输入时会发生这种情况,这表现为:

顺序反馈回路

两个逆变器或NOT被连接在与输出串联栅极Q反馈到输入端。不幸的是,这种配置永远不会改变状态,因为输出将始终是相同的,无论是“ 1”还是“ 0”,它都是永久设置的。但是,我们可以通过检查最基本的顺序逻辑组件(称为SR触发器)来了解反馈的工作原理。

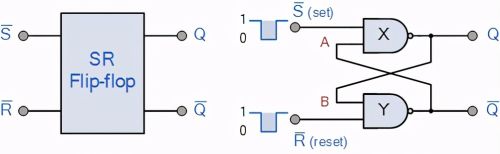

SR触发器

所述SR触发器,也称为SR锁存器,可以被认为是最基础的时序逻辑电路可能之一。这个简单的触发器基本上是一个具有一个位的存储器双稳态器件,具有两个输入,一个输入将“设置”该设备(表示输出=“ 1”),并标记为S,另一个标记为“复位”该设备。 (意味着输出=“0”),标记为[R 。

然后,SR描述代表“设置-重置”。复位输入使用输出Q将触发器复位到其原始状态,该输出Q将根据设置/复位条件为逻辑电平“ 1”或逻辑“ 0”。

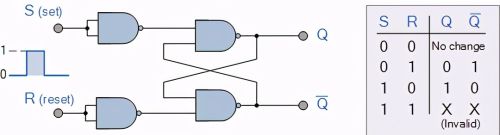

基本的NAND门SR触发器电路将两个输出的反馈都反馈到其相对的输入,通常用于存储电路中以存储单个数据位。然后,SR触发器实际上具有三个输入,即Set,Reset和与其当前状态或历史有关的当前输出Q。术语“触发器”涉及设备的实际操作,因为它可以“翻转”为一种逻辑设置状态或“翻转”为相反的逻辑复位状态。

NAND门SR触发器

制作任何基本的单比特置位复位SR触发器的最简单方法是将一对交叉耦合的2输入NAND门连接在一起,以形成置位复位双稳态,也称为有源LOW SR NAND门。锁存,以便从每个输出到其他NAND门输入之一的反馈。该器件由两个输入组成,一个称为Set,S,另一个称为Reset,R,具有两个对应的输出Q及其反或补Q(非Q),如下所示。

基本SR触发器

设定状态

考虑上面显示的电路。如果输入R处于逻辑电平“ 0”(R = 0)并且输入S处于逻辑电平“ 1”(S = 1),那么与非门Y 的输入之一至少为逻辑“ 0”,其输出Q必须为逻辑电平“ 1”(与非门原理)。输出Q也被反馈到输入“ A”,因此“与非”门X的两个输入均处于逻辑电平“ 1”,因此其输出Q必须处于逻辑电平“ 0”。

再次是“与非”门原理。如果复位输入R改变状态,并在逻辑电平为“ 1”时S保持高电平的状态下变为逻辑“ 1”,则与非门Y输入现在为R =“ 1”且B =“ 0”。由于其输入之一仍为逻辑电平“ 0”,因此Q处的输出仍为逻辑电平“ 1”时保持高电平,并且状态不变。因此,触发器电路被称为“锁存”或“置位”,且Q =“ 1”且Q =“ 0”。

重置状态

在此第二稳定状态下,Q处于逻辑电平“ 0”(不是Q =“ 0”),其在Q处的反向输出处于逻辑电平“ 1”(Q =“ 1”),由R = “ 1”且S =“ 0”。由于门X的输入之一为逻辑“ 0”,因此其输出Q必须等于逻辑电平“ 1”(再次与非门原理)。输出Q反馈到输入“ B”,因此“与非”门Y的两个输入都为逻辑“ 1”,因此Q =“ 0”。

如果设置的输入S现在将状态更改为逻辑“ 1”,而输入R保持为逻辑“ 1”,则输出Q仍保持为逻辑“ 0”,并且状态不变。因此,触发器电路的“复位”状态也已被锁存,我们可以在下面的真值表中定义此“设置/复位”动作。

设置复位功能的真值表

州

小号

[R

问

问

描述

组

1个

0

0

1个

设置Q »1

1个

1个

0

1个

没变化

重启

0

1个

1个

0

重设Q »0

1个

1个

1个

0

没变化

无效

0

0

1个

1个

无效条件

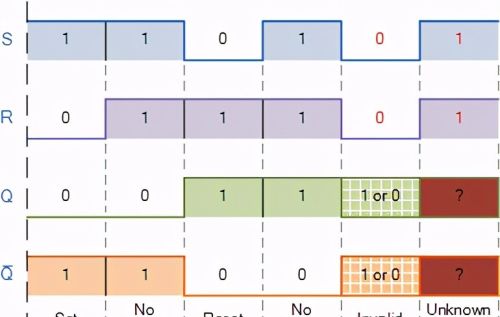

可以看出的是,当两个输入小号=“1”和- [R =“1”的输出Q和Q可以在任一逻辑电平“1”或“0”,这取决于输入的状态小号或- [R在此之前输入条件存在。因此,S = R =“ 1”的条件不会改变输出Q和Q的状态。

但是,S =“ 0”和R =“ 0”的输入状态是不希望的或无效的条件,必须避免。的条件S = - [R =“0”使得两个输出Q和Q为HIGH一起是处于逻辑电平“1”时,我们通常会希望Q是的逆Q。结果是触发器失去了对Q和Q的控制,并且如果在此条件之后将两个输入再次切换为“高”,则逻辑为“ 1”,则触发器将变得不稳定,并基于以下状态切换为未知数据状态:如下开关图所示。

SR触发器开关图

这种不平衡会导致其中一个输出的切换速度比另一个输出的切换速度快,从而导致触发器切换到一个状态或另一个状态,而这可能不是必需的状态,并且会存在数据损坏的情况。这种不稳定状态通常称为其亚稳态。

然后,可以通过将逻辑“ 0”,(LOW)条件施加到其置位输入来设置简单的“与非”门SR触发器或“与非”门SR锁存器,然后通过将逻辑“ 0”应用于其复位输入来再次进行复位。如果置位和复位输入均被同时激活,则SR触发器被称为处于“无效”状态(亚稳态)。

如上所述,基本的NAND门SR触发器需要逻辑“ 0”输入才能将状态从Q翻转到Q或反之亦然。但是,我们可以将这种基本的触发器电路更改为通过施加正向输入信号来改变状态的电路,并添加两个额外的与非门,作为反相器连接到S和R输入,如图所示。

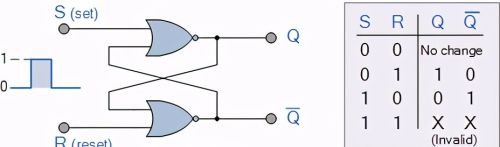

正与非门SR触发器

除了使用“与非”门外,还可以使用以相同配置连接的两个交叉耦合的“或非”门构造简单的一位SR触发器。该电路将以与上述NAND门电路类似的方式工作,不同之处在于,输入为高电平有效,并且当两个输入均为逻辑电平“ 1”时,存在无效条件,如下所示。

或非门SR触发器

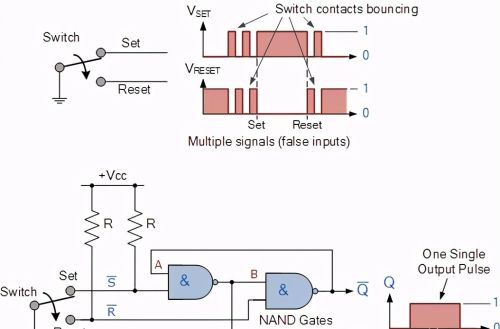

开关去抖电路

边沿触发的触发器需要良好的干净信号转换,这种置位复位电路的一种实际用途是用作锁存器,以帮助消除机械开关的“反弹”。顾名思义,当操作任何机械操作的开关,按钮或小键盘的触点且内部开关触点未完全闭合时会发生开关弹跳,但是在按下开关时先合弹,然后再闭合(或断开) 。

这会产生一系列单个脉冲,这些脉冲可能长达数十毫秒,电子系统或电路(例如数字计数器)可能会视为一系列逻辑脉冲,而不是一个较长的单个脉冲,并且行为不正确。例如,在该反弹期间,输出电压可能会剧烈波动,并且可能会记录多个输入计数,而不是一个计数。然后,可以使用置位复位SR触发器或双稳态锁存电路来消除此类问题,下面对此进行说明。

SR触发器开关去抖电路

根据输出的当前状态,如果按下设置或重置按钮,则输出将以上述方式进行切换,并且开关机械作用产生的任何其他多余输入(反弹)都不会影响输出。Q。

当按下另一个按钮时,最先的接触将导致闩锁改变状态,但是任何其他机械开关弹跳也将无效。然后,可以在短时间(例如0.5秒)后自动将SR触发器复位,以便注册来自同一开关触点的任何其他有意重复输入,例如键盘“ RETURN”键的多个输入。

MAX6816,单输入,MAX6817,双输入和MAX6818八路输入开关去抖动器IC是专门为克服开关抖动问题而专门制造的通用IC。这些芯片包含必要的触发器电路,以提供机械开关与数字系统的干净接口。

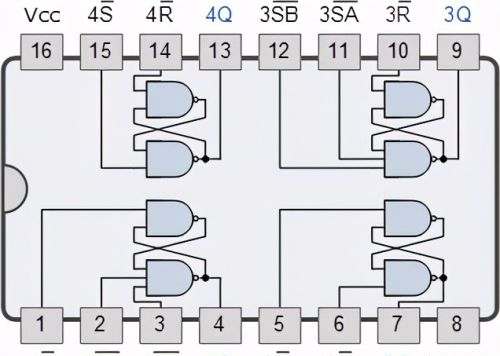

置位-复位双稳态锁存器还可以用作单稳态(单脉冲)脉冲发生器,以产生某个指定宽度或时间段的高或低单个输出脉冲,以用于定时或控制目的。74LS279是一个Quad SR双稳态锁存IC,在单个芯片中包含四个单独的NAND型双稳态,可轻松构建开关去抖动或单稳态/稳定时钟电路。

Quad SR双稳态闩锁74LS279

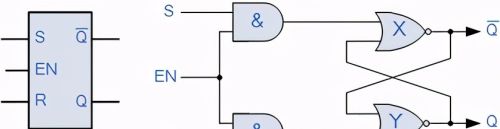

门控或时钟SR触发器

有时在顺序逻辑电路中希望有一个双稳态SR触发器,该触发器仅在满足某些条件时才改变状态,而与置位或复位输入的条件无关。通过将2输入与门与SR触发器的每个输入端子串联连接,可以创建门控SR触发器。此额外的条件输入称为“启用”输入,并以“ EN ”作为前缀。此输入的增加意味着Q处的输出仅在其为HIGH时才改变状态,因此可以用作时钟(CLK)输入,使其对电平敏感,如下所示。

门控SR触发器

当使能输入“EN”为逻辑电平“0”,两者的输出与门也处于不管两个输入的条件的逻辑电平“0”,(与门原则)小号和- [R ,锁存两个输出Q和Q进入最后一个已知状态。当使能输入“ EN”变为逻辑电平“ 1”时,电路将作为正常的SR双稳态触发器作出响应,两个“与”门对置位和复位信号透明。

该附加的使能输入也可以连接到时钟定时信号(CLK),从而将时钟同步添加到触发器,从而创建有时称为“时钟SR触发器”的时钟。因此,门控双稳态SR触发器用作标准双稳态锁存器,但仅在逻辑“ 1”施加到其EN输入并被逻辑“ 0”禁用时才激活输出。