为什么RFSOI技术更适合波束成形IC?

本文编译自everythingrf

相控阵天线已证明其对毫米波 5G 无线电的重要价值。波束聚焦的改进,波束范围的增强提高了数据吞吐量与定向波束控制提供的空间复用性。使用具有独特幅度和相位设置的每个天线的信号来驱动这些天线阵列,往往需要非常复杂的电路,分发模拟波束成形 IC,将它们放置在天线元件阵列内的阵列中,已被证明具有高度可制造性、低射频信号损耗和总体成本效益等优势。

然而,这些波束成形 IC (BFIC) 的实施受到了一些限制,部分原因在于半导体技术,包括体 CMOS、SiGe、GaAs 和 GaN都无法同时满足BFIC的需求。 目前,业界普遍认可RFSOI 是全面优化 BFIC 的基础,并为 5G 和其他应用(例如平板电子可控卫星通信天线)提供了更高性能和更低成本的相控阵天线系统。在 5G 基础设施中,这些性能优势进一步扩展,以降低网络部署和 OPEX 成本。

RFSOI与其他硅制程

首先,让我们将 RFSOI 与迄今为止用于 BFIC 的其他硅工艺(体 CMOS 和 SiGe)进行比较。与这些替代硅技术相比,RFSOI 具有几个关键的基本优势。 RFSOI 中的“SOI”代表“绝缘体上的硅”。在 SOI 中,有源层下方的半导体硅衬底被绝缘氧化物取代。高电阻绝缘基板减少了电路几个关键区域的寄生效应,并允许晶体管之间更高的隔离度。由于毫米波频率下的高损耗,有源和无源元件中的寄生效应都至关重要。

FET 结和 FET 周边的较低寄生效应允许晶体管速度更快。例如,GlobalFoundries 45RFSOI 器件的 Ft 和 Fmax 分别为 305 和 380 GHz。这远高于体 CMOS 所达到的 200 GHz。除了高晶体管速度(这当然对毫米波工作频段非常有帮助)之外,减少寄生效应还可以提高无源元件的品质因数并降低损耗。BFIC 需要一个复杂的路由网络,收发器需要通过放大器、衰减器和移相器。SOI 允许更低损耗的传输线、匹配网络、分离/组合和滤波器结构。对这些结构的改进可显着降低射频链中的信号损失。由此产生的损耗降低会推动链中放大器对增益和射频输出功率的要求降低,从而提高整体功率效率。

RFSOI 与 III-IV 的对比

其次,将 RFSOI 与传统的 III-V 族化合物半导体进行比较。由于高载流子迁移率和晶体管击穿电压,GaAs 和 GaN 等化合物半导体比硅工艺具有更好的原始射频性能优势。然而,它们有几个缺点,使 RFSOI 在这些应用中保持优势。这些缺点包括低集成度、较高的成本以及更高的射频功耗。

考虑电路集成:GaAs 和 GaN 等 III-V 族化合物半导体在某些(但不是所有)情况下可以集成放大器功能(如 PA 和 LNA),但无法实现完整的射频前端集成。这些集成限制通常最终迫使使用单独的(基于硅的)配套 IC 来实现关键功能。 RFSOI 则允许在 RF/mmWave、模拟和数字域中通过单芯片集成实现极高的集成度。

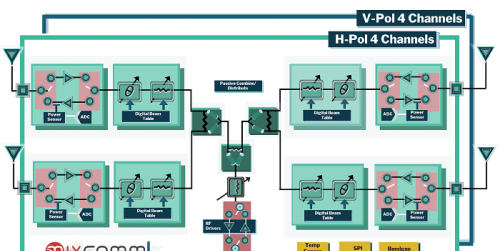

带有集成功率放大器和低噪声放大器的 Tx 和 Rx 链

低损耗射频开关

偏置、增益和相位的复杂控制电路更容易在硅中实现

数字控制、SPI 和 LVDS、片上 Beam Table 存储存储器

数模 DAC 和模数 ADC 转换

模拟功能,例如温度和功率感应

用于 5G 相控阵天线的化合物半导体解决方案也受到更高系统成本的影响。 III-V GaAs 和 GaN 芯片的生产成本本来就更高。与 RFSOI 的 300 毫米相比, III-V所采用的的75、100 或 150 毫米的晶圆尺寸更小,加上相对奇特且昂贵的基板材料,导致每平方毫米的成本更高。此外,GaAs 和 GaN 若要实现最佳的射频功率水平可能会迫使使用额外的分配网络将信号能量发送到多个天线元件——增加损耗、PCB 复杂性和成本。

RFSOI 的优势转化为更高的 BFIC 性能

我们概述的优势表明,RFSOI 与 III-V 和替代硅技术(如体 CMOS 和 SiGe)相比具有多项优势,但这如何转化为毫米波的优势?我们已经谈到了如何降低无源结构中的损耗可以提高射频系列的效率。此外,RFSOI,BFIC其他几个方面还可以实现改进。虽然它确实需要多年的开发,但优化的构建模块,如功率放大器、低噪声放大器,以及由 RFSOI 独特启用的波束形成增益和相位控制电路,可以在每个通道中提取更高的效率和更高的线性射频功率水平。

更高的隔离度 = 更高的线性射频功率和更高效的功率放大器

RFSOI 提供的晶体管之间改进的隔离使得功率放大器和 RF 开关中的晶体管器件能够“堆叠”,以允许更高的电压操作。在功率放大器中,这意味着更高的电源电压和更高的输出阻抗,从而减少匹配损耗并提高工作效率。鉴于 BFIC 中的大部分功耗发生在 Tx 模式期间的功率放大器中,这里的效率提高意味着整体无线电效率的显着提高。更高的电压摆幅还实现更高的线性射频输出功率能力,允许 BFIC 的每个通道向相关的天线元件提供更多的射频功率。

对于在 TDD 中运行的 5G 系统,BFIC 必须有多个射频开关才能在 Tx 和 Rx 模式之间切换。在 TDD 开关中,RFSOI 的晶体管隔离也允许晶体管堆叠。在开关中,这允许增加开关引脚上的电压摆幅、更好的开关隔离以及更低的损耗,同时保持低 Ron*Coff 品质因数。

更好的 BFIC 意味着更好的阵列天线

基于RFSOI 的改进型波束形成器 IC 可以改进可控相控阵天线及其在毫米波 5G 中的应用。来自这些 BFIC 的每通道更高的线性射频Tx 功率,意味着更少的天线元件就可以实现整个阵列所需的 EIRP(辐射功率)目标。天线阵列可以优化以平衡增益、Rx 灵敏度和扫描性能。更少的天线元件也意味着更小的天线尺寸和更少的 BFIC。同时拥有更小的电路板和更少的组件可降低系统 BOM 成本。

这些优化的 BFIC 提高的效率也对阵列天线成本产生了影响。通过降低总功耗,废热管理要求也随之降低。散热器的尺寸和重量可以减小,从而减少最终产品的物理尺寸。RFSOI BFIC 的更高线性功率和更高效率允许更小、更便宜、更漂亮的收发机,从而更容易隐藏在建筑物或街道设施的一侧。

AiP——毫米波天线阵列的“圣杯”

优化基于 RFSOI 的低功耗 BFICS 也支持独特的阵列实施。封装内天线 (AiP) 的前景早已得到认可,因为它允许将天线阵列以经济高效的方式直接集成到 BFIC 周围的封装中。 AiP 可以在比标准 PCB 技术更高的频率下实现最佳天线间距。它还可以允许 BFIC 和天线元件之间的低损耗连接。最后,AiP 模块可以在天线平面上实现预先编程增益和相位校准,从而减少或消除对最终产品校准的需求,可以降低成本。如果没有真正高效的 BFIC 提供的较低功耗,AiP 封装概念会随着电路的实际工作而分崩离析——缩短电路寿命并威胁封装叠层的机械完整性。

除了减少校准测试时间之外,AiP 还以其他方式降低系统成本。通过在模块内放置最敏感的布线,可以使用容差较低的 PCB 工艺,这减少了对PCB 供应商的依赖。安装 AiP 的 PCB 现在也可以使用较少的昂贵低损耗层。最后,通过承担设计中最困难的部分、天线元件和 BFIC 接口,AiP 可以从根本上减少新毫米波天线系统的工程挑战、开发时间和成本。

MixComm ECLIPSE3741:39 GHz AiP,左侧有 16 个元件天线阵列,右侧有四个 双极BFIC

更好的阵列天线带来更好的网络部署

首批部署的使用体 CMOS 和 SiGe 等其他技术的 mmWave 5G 相控阵天线在多个领域都存在不足。它们的效率非常低,这增加了运营成本并产生了严重的散热问题。这些波束形成器 IC 的每通道线性输出功率也非常低。这意味着非常大的 IC 和天线阵列必须开发 NAS 以达到目标辐射功率。当然,从成本、尺寸和美学的角度来看,这也是不可取的。事实上,在不影响扫描角度等其他性能因素的阵列尺寸内,其中一些阵列根本无法满足所需的 EIRP 水平。

由基于 RFSOI 的 BFIC 支持的更好阵列导致具有小型阵列和小型散热器的更小、更轻的天线。这些缩小的维度以多种方式改进了部署,更少的重量意味着更低的附件成本。较小的天线在美学上也更好,并且更容易隐藏,使它们更受当地监管机构的欢迎。

更好的毫米波天线阵列实施也可以达到 FCC 规定的辐射功率限制。更高的辐射功率和覆盖范围意味着需要更少的无线电——这可以迅速增加系统部署成本的节省。

5G 毫米波:准备充分发挥其潜力

RFSOI 是一项基础技术,具有许多毫米波固有的优势。充分利用这些优势的优化毫米波构建模块可实现更高性能的波束成形 IC。更高性能的 BFIC 允许使用更小、更便宜的相控阵天线,包括在 AiP 实施中体现的最简单和最低成本等。通过在强大的 RFSOI 基础上逐层构建,我们能够看到使毫米波 5G 部署能够发挥其真正潜力的系统。

深度好文:为什么RFSOI技术更适合波束成形IC?-电子工程世界