MCU中有多少种存储器

MCU 中内部存储器的数量取决于存储器的分类方式。主要有两种存储器:随机存取存储器(RAM)和只读存储器(ROM)。但是,根据内存性能不同,RAM 和 ROM 有不同的类型。这些不同类型的存储器可用于各种功能,例如高速缓存、主存储器、程序存储器等。另一方面,存在内存的虚拟与物理定义的问题。

RAM 的两种主要类型是静态随机存取存储器 (SRAM) 和动态随机存取存储器 (DRAM)。两者都需要施加电压来保存它们的信息。DRAM 很简单,基本实现只需要一个晶体管和一个电容器。DRAM是所有内存技术中使用最广泛的一种。当集成到 MCU 中时,它被称为嵌入式 DRAM (eDRAM)。与用作外部存储器的等效独立 DRAM 芯片相比,eDRAM 的每比特成本更高。尽管如此,将 eDRAM 放置在与处理器相同的芯片上的性能优势仍超过了高性能应用中的成本劣势。

SRAM 比 eDRAM 更复杂,通常由六个晶体管实现。 SRAM 比 DRAM 更快,因此非常适合集成到 MCU 中。它是最常用的内部 MCU 内存技术之一。 SRAM 通常用作高速缓存和处理器寄存器。

MCU 中的非易失性存储器包括闪存和电可擦可编程 ROM (EEPROM)。闪存是 EEPROM 的一种形式。它们之间的主要区别在于它们的管理方式; Flash 在块级别进行管理(写入或擦除),而 EEPROM 可以在字节级别进行管理。闪存可用于 NAND 和 NOR 架构。 NAND 闪存以块为单位处理数据,读取速度快于写入速度。它可以快速传输多页数据。它提供比 NOR 更高的单位面积容量,用于高密度存储。NOR Flash支持更细粒度的操作,并提供高速随机访问。NOR Flash可以读写特定的数据。

Fujio Masuoka 在 1980 年代在东芝工作时发明了闪存。他的同事 Shoji Ariizumi 使用 Flash 一词来描述新技术,因为擦除所有数据让他想起了相机的 Flash。易失性和非易失性存储器技术可以根据几个性能标准进行比较:

速度:易失性内存通常更快

成本:易失性内存成本更低

寿命:易失性存储器的寿命更长。非易失性存储器由于其重写能力而具有有限的寿命。

能耗:DRAM等易失性存储器需要重复数据刷新,这会消耗额外的功率。非易失性存储器通常消耗较少的功率。

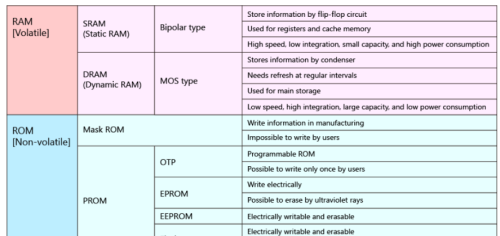

表 1:多种类型的 RAM 和 ROM 存储器提供特定的性能权衡。(来源:东芝)

内存层次结构

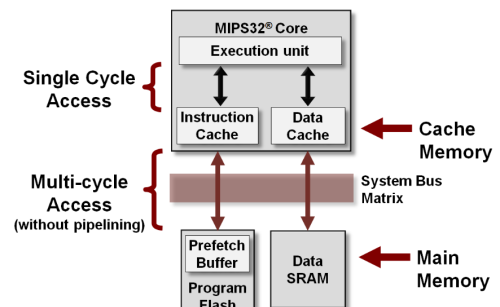

高速缓存是 MCU 中的关键系统。有两种方法可以对高速缓存进行分类:层次结构或功能。当按照层次结构进行描述时,最多可以有 4 级高速缓存。高速缓存由快速存储器组成,例如 SRAM 和 eDRAM,以补偿主 Flash 存储器较慢的访问时间。 1 级高速缓存是一小块内存,可以与 CPU 一样快地运行以支持最大处理速度。 2 级和 3 级缓存支持 1 级缓存。它们比 1 级缓存更大、但是慢一些,不过依然比主内存快(图 1)。

图 1:处理器和主存储器之间的高速缓存集,以提供支持高效处理器操作所需的更快访问时间。

在性能和大小方面,eDRAM 位于内存总线上的 3 级缓存和传统 DRAM 之间,用作 4 级缓存。与 SRAM 相比,更高密度的 eDRAM 可以支持更宽的总线和更高的运行速度。与 SRAM 相比,更大量的 eDRAM 可以集成到更小的区域中。制造 eDRAM 比 SRAM 更复杂,但是当需要大量内存时,eDRAM 节省的 3 倍面积可以抵消制造成本。

对于任何给定级别的高速缓存,所有块都具有相同的大小和关联性。像 1 级缓存这样的较低级别具有更少且更快的块。随着级别增加到 2 和 3,缓存内存的块数越来越多,块大小越来越大,而且一组中的块也越来越多。但是每一级高速缓存都比主存快得多。除了主缓存外,特殊类型用于特定功能。示例包括:

管道缓存。例如,在 RISC MCU 中,流水线 CPU 从流水线中的多个点访问内存,包括数据提取、指令提取和虚拟到物理地址转换。管道使用三个专用缓存:数据、指令和转换缓冲区 (TLB)。

牺牲缓存。已从 CPU 缓存中替换和删除的数据块保存在牺牲缓存中。牺牲缓存设置在主缓存和重新填充路径之间。它是完全关联的,旨在减少可以从高度关联映射中受益程序的冲突未命中次数。在一些实现中,4 级缓存可以用作牺牲缓存。

微操作缓存。该高速缓存存储从指令高速缓存或指令解码器接收到的已解码指令的微操作。它可以加快处理速度。当指令需要解码以查看其解码形式是否已经可用时,检查微操作缓存。如果它在微操作缓存中不可用,则该指令将被解码并缓存以供将来使用。

内存组织和 MCU 架构

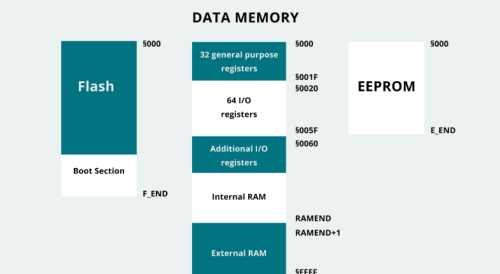

不同的 MCU 类型,例如 AVR 和 ARM 架构,使用不同的方式来组织内存。基于哈佛的 AVR 架构将内存拆分成闪存、内部和外部 DRAM 以及 EEPROM(图 2)。因此,使用这些 MCU 的系统将内存组织成特定的部分,包括:

文本部分包含加载到闪存中的指令;数据部分包含已初始化的变量,BSS 包含未初始化的数据,堆栈包含函数和中断的数据,堆包含运行时创建的变量。

图 2:在基于哈佛的 AVR 微控制器中,存储器分为闪存(左)、内部和外部 DRAM(中)和 EEPROM(右)。

在 ARM MCU 中,内存映射与 32 位、36 位和 40 位的不同地址配置一起使用,具体取决于系统地址空间和额外 DRAM 的要求。内存管理单元 (MMU) 控制内存访问指令,这些指令可用于高级代码以管理中断模块和集成外设。

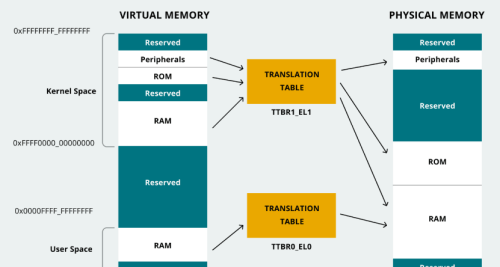

MMU 的主要目的是使处理器能够在虚拟内存空间中独立运行多个任务。 MMU 使用转换表来桥接虚拟和物理内存地址。虚拟地址通过带有内存指令的软件进行管理。物理地址根据虚拟地址给出的转换表输入进行控制(图 3)。

图 3:在混合 ARM 处理器中,转换表在虚拟内存和物理内存之间进行映射。 (图片:阿杜诺)

MMU 是一个专门的内存单元,包括从内存中读取翻译表的单元和缓存最近使用的翻译的 TLB。 CPU 软件中的所有内存地址都是虚拟的。 MMU 检查 TLB 是否有最近缓存的翻译。如果不存在,table walk 单元从内存中读取适当的表条目。

总结

MCU 包括各种形式的 RAM 和 ROM,以支持特定的性能要求。 MCU 中最常见的存储器形式包括 eDRAM 和 SRAM 易失性存储器以及闪存和 EEPROM 非易失性存储器。 Flash 和 EEPROM 一般用于主存储器,而 eDRAM 和 SRAM 用于各种高速缓存功能。此外,MCU 存储器基于虚拟和物理地址和功能进行组织,并通过 MMU 进行管理。