如何快速洞察PCIe发送端链路健康状况?

传统上,发送端(Tx)测试一直要求使用示波器,来测量被测器件(DUT)发送信号的眼高和眼宽,以评估信号质量。作为验证一致性测试系统一贯指定的工具,示波器被大量用于开发工作中,来确定DUT是否能通过许多高速I/O(HSIO)标准一致性测试认证。尽管示波器对开发和调试非常关键,但为了更快洞察发送端链路健康状况,业界正越来越多地需要其他设备,来缩短示波器的测试时间。

本文介绍实际案例,演示泰克全新的TMT4 PCIe性能综合测试仪发送端测试方法,如何为PCIe板卡和系统设计提供可操作的测试见解。

BIOS设置和互操作能力

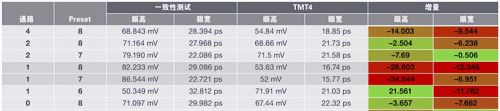

泰克与客户密切合作,发现在多种案例中,TMT4 PCIe性能综合测试都可以传统测试系统和一致性测试进行补充。在第一个案例中,某主板制造商试图改变被传统一致性测试测量的BIOS设置,以优化信号质量。下表显示,通路0到通路4默认的BIOS设置和更新后的BIOS设置的眼宽和眼图均通过测试,测得结果略有变化。

表1. 原始BIOS设置和更新后的BIOS设置的一致性测试结果

尽管如此,该主板制造商在更新的BIOS设置里开始出现互操作问题,而以前在默认设置里是没有的。由于这两种一致性测试结果之间差异已经最小化,该制造商不确定是什么导致了问题,也不确定为什么使用自己的测试系统时这两种配置都通过了测试。

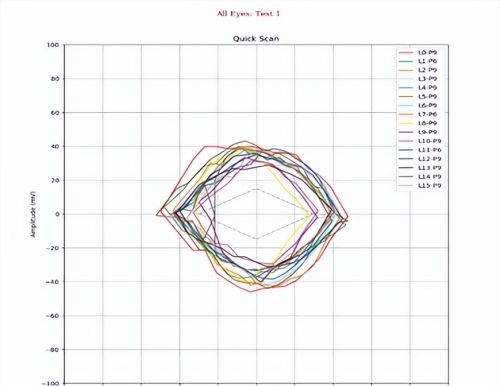

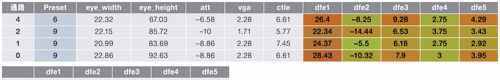

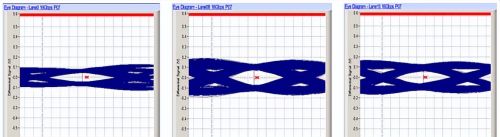

泰克公司与该制造商合作,看看TMT4 PCIe性能综合测试是否能够得到任何有用的信息,而这些信息是其测试系统的结果中没有显示的。开始前,TMT4先使用默认BIOS设置运行了快速扫描,它发起自然链路协商,用了5分钟的测试时间,来查看能找到什么信息。下面几个图是眼图、链路训练参数以及格式化表格使用的可能的DFE抽头值的范围。

图1. 默认BIOS设置的快速扫描图

表2. 链路训练参数和DFE阶范围

前4条通路的数据提取自链路训练参数表,以便与上面的BIOS设置结果子集进行对比,DFE抽头值则根据每个DFE抽头的上下限有地条件格式化在Excel电子表格中。显而易见的是,PCIe性能综合测试并没有训练到根据缺省BIOS设置而变化的哪些Preset上。这表明TMT4和DUT之间协商到的Preset并不在与BIOS变化有关的诸Preset中。

此外,我们可以清楚地看到,DFE的抽头1被很大力度地使用以张开眼图,这表明接收端正在使用很大的均衡以便形成链路。因此,当链路能够形成时,另一个接收端裕量差的DUT很可能会引发互操作能力问题。

由于DUT并不会自然地训练到BIOS表中指明的通路和Preset设置,因此我们使用TMT4运行自定义扫描,查看DUT中的所有通路-Preset组合。在大约30分钟后,TMT4收集到了下面的眼图和链路训练参数表。

图2. 默认BIOS设置的自定义扫描图

表3. 默认BIOS设置自定义扫描图的链路训练参数

与之前的快速扫描结果一样,我们缩减了链路训练参数表,仅仅比较我们评估的BIOS设置子集。同样,很容易就看出DFE被用于张开眼图的力度有多大,特别是来自DFE的抽头1、抽头2、抽头5。同样令人感兴趣的是一致性测试结果与TMT4结果测得的眼高和眼宽的差异,如下表所示。

表4. 眼高和眼宽测量数据对比—一致性测试和TMT4

我们再次使用Excel电子表格中的有条件格式化,这个表格直观地展示了一致性测试结果与TMT4结果之间有意义的差异。特别是,对于眼高和眼宽来说,使用P7和P8的通路在使用真实链路流量的TMT4结果,看上去要比使用测试信号的一致性测试结果要糟糕得多。整体上,由于严重依赖均衡来张开眼图,无论是在快速扫描结果和自定义扫描结果中,这个DUT发生互操作问题的机率都很高。

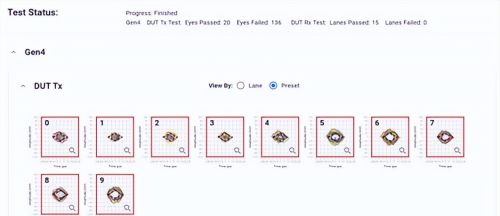

接下来,我们使用TMT4评估更新后的BIOS设置,看能得到什么。与前面一样,该制造商发现在更新设置后,TMT4与DUT不能形成链路,因此不能扫描结果,如下面的截图所示。

图3. TMT4 Web UI截图—使用更新后的BIOS设置没有形成链路

虽然根据该制造商在更新BIOS设置后已经看到的互操作问题,这个结果是意料之中的;当查看到在缺省设置中使用DFE的力度有多大,这个结果并不让人吃惊。它表明,更新BIOS设置使得链路严重到足以导致了互操作问题,特别是DUT试图与没有良好的接收端裕度的对端进行互操作时。

在短短30分钟测试中,通过对导出的结果进行基本的Excel格式化,TMT4能够为这家制造商提供关于张开发送信号眼图所需的均衡水平,以及复现其遇到的互操作问题等额外的信息。这个简单案例说明了TMT4可以很好地对传统一致性测试进行补充,特别是在一致性测试通过,但在设计中仍遇到互操作能力问题时。

重驱动器增益设计和互操作能力

另一家主板制造商试图解决重驱动器增益设置中遇到的问题。他们采用芯片厂商提供的参考设计,在使用泰克TekExpress软件和示波器时通过了测试,如通路0、8、15的结果如下面几个图所示。

图4. Tek Express对重驱动器设置通路0、8、15的眼图截图

尽管结果通过了测试,但这家制造商仍然遇到了互操作问题,而又找不到根本原因。泰克科技为他们提供了一个机会,使用TMT4帮助他们调试这个问题。TMT4经历了在Gen4速度下DUT遇到的互操作问题,如下面的截图所示。

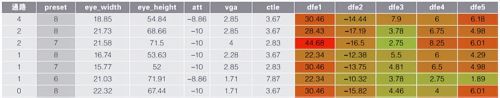

图5. TMT4 Web UI截图—重驱动器设置在Gen 4速度下没有形成链路

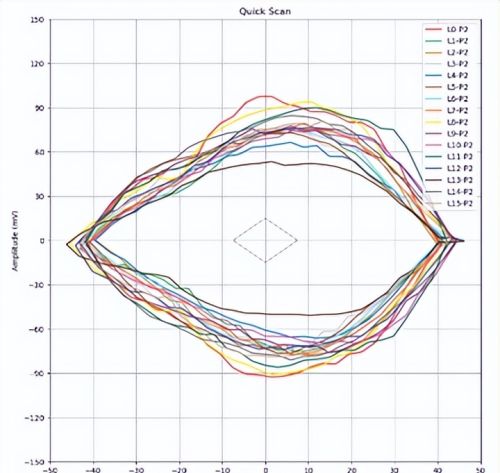

在Gen 4速度下未能形成链路后,TMT4被调整以在 Gen 3速度下测试DUT。在调节到Gen 3速度后,TMT4能够与DUT形成链路。通过在Excel电子表格中进行一些基本分析,这家制造商能够轻松地可视化问题发生在哪里。如下表所示,几乎不需要均衡就能把插槽的高8条通路上的眼图张开,但低8条通路上有一些通路有问题,如红字所示。

图6. 在 PCIe Gen 3速度下重驱动器设置的链路训练参数表和快速扫描眼图

大家注意到,通路8-11使用的DFE抽头1的均衡要远超其他通路。这就快速地向制造商表明,与通路0-7相比,链路另一端的接收端不得不使用更大的均衡以便张开通路8-15的眼图。在通路13上,大家注意到,不需要太大的均衡就能张开眼图,但这明显小于所有其他通路,特别是与通路0相比,通路13的均衡量几乎只有一半。

在短短5分钟快速测试后,TMT4就向这家制造商指明,互操作外推可能出现在重驱动器设计的后8条通路中,因为通路8-15中的DFE均衡更大,眼图更小。