> 美食

时钟逻辑电路(时钟逻辑电路设计)

时钟逻辑类型接口-LVPECL简述

前一篇文案介绍了LVDS,本篇介绍LVPECL(Low Voltage Positive Emitter Coupled Logi) 低压正射极耦合逻辑, 源自发射极耦合逻辑(ECL),采用正电源。

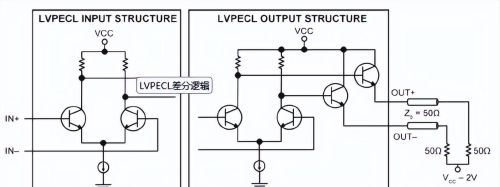

输入是具有高输入阻抗的电流开关差分对。输出由差分对放大器组成,驱动一对射极跟随器。如下:缺点是功耗相对较高以及有时需要提供单独的终接电压轨技术能实现超过10Gbps的高数据率。

LVPECL输入与输出端功能框图

LVPECL内部工作原理LVPECL差分输出端分别50Ω传输阻抗至Vcc-2V和输出总线OUT + / OUT-输出为中间电平为:Vcc-1.3V,导致近似的直流电流为14mA。

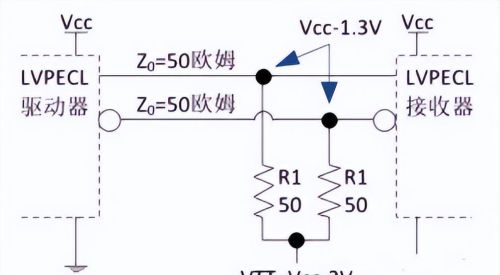

LVPECL端接匹配网络最简单的LVPECL匹配方式就是在接收器的输入侧需要一个参考电压:Vcc-2V,如下

典型配置方式

额外的电源需求会增加电路的复杂度和成本,本案介绍几种常用端接方式(参见:浅谈LVDS、CML、LVPECL三种差分逻辑电平之间的互连-电子发烧友),如下为推荐:

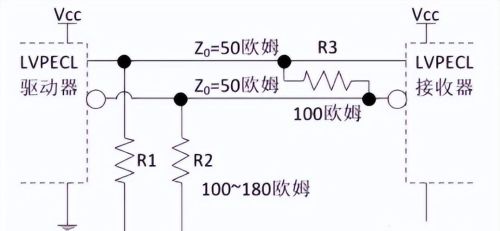

直流耦合三电阻方式

R1=140~200欧姆(Vcc:3.3V),R1=270~330欧姆(Vcc: 5V),R2=100欧姆。R1为输出门提供偏置电流,R2为交流信号提供匹配。输入门的直流电平偏置直接利用输出门的直流电平(Vcc-1.3V),并不需要外来的上下拉电阻来提供。R2一个电阻必须放在离输入门比较近的地方,R1放置的地方可以比较随便。

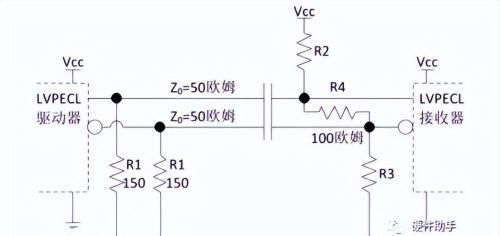

交流耦合

R1=140~200欧姆,属于直流偏置电阻。C1为耦合电容,可以放在线上的任何一个地方。R4=100欧姆,属于交流匹配电阻,一定要放在末端。R2、R3为K级别的电阻,必须满足R3/(R2+R3)=(VCC-1.3V)/VCC的比值就可以了,这两个电阻是为输入端提供直流电平,所以对PCB上的位置没有特殊要求。

温馨提示:通过以上关于时钟逻辑类型接口-LVPECL简述内容介绍后,相信大家有新的了解,更希望可以对你有所帮助。