mosfet场效应晶体管特点(场效应晶体管mos)

MMIC电路设计中的场效应晶体管(FET)技术介绍

场效应晶体管(FETs)的结构和操作

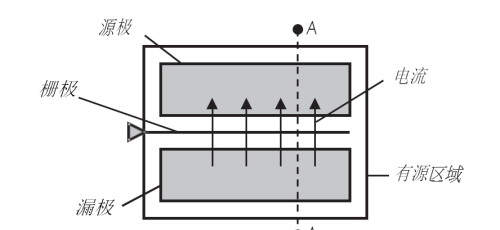

FETs的俯视图,如同俯视MMIC晶圆表面,如图1所示。电流横向流过晶圆表面,从漏极到源极,并在栅极接触下通过。

图1、场效应晶体管(FET)的俯视图

注意,这只是单个栅极FET(或基本单元),并且这种器件,尤其是功率FET,由多个栅极指状物构成(以后我们会更详细地介绍)。

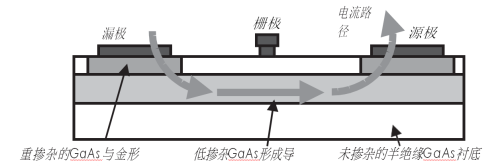

图1中FET的截面图“A-A”如图2所示,FET形成有半导体的低掺杂层,其在晶片表面下方形成导电沟道(channel),如图2(a)所示。沟道通常是n掺杂的,因此存在自由电子以在沟道中传输电流。金属源极和漏极端子通过欧姆接触与该导电沟道接触到半导体的重掺杂层。如果在漏极和源极触点之间放置电压,则电流可以在它们之间流动,直到沟道(channel)中的所有自由电子都传导电流为止。如果栅极端子上的电压为零,则该电流称为漏源饱和电流(IDSS)。这是场效应晶体管的“导通”状态。

(a)

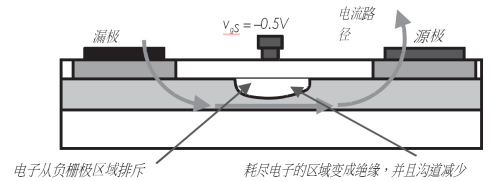

(b)

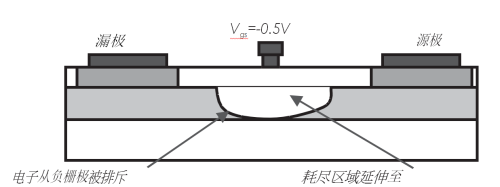

(c)

图2、场效应晶体管(FET)的截面图,其中(a)栅极为0V,(b)栅极为-0.5V,(c)栅极为-1.0V,相对于源极电压。由于栅极上没有电压,电流可以从漏极流向源极。栅极上的负电压很小,电流减小。栅极上的负电压很大,电流停止,晶体管关闭(称为夹断,因为沟道被夹紧闭合)。

如果相对于源极电压(Vgs)的小负电压施加到栅极端子,如图2(b)所示,沟道内的带负电的电子将从栅极和沟道(channel)的一个区域排斥,被称为耗尽区中的自由电子耗尽。耗尽其自由电子的一些沟道(channel)的效果是仅沟道(channel)的底部具有自由电子来传输电流,因此流过沟道(channel)的最大电流减小。如果如图2(c)所示将更大的负电压施加到栅极端子(Vgs),则电子甚至更远离栅极被排斥,并且耗尽区域一直延伸穿过沟道。当耗尽区一直延伸穿过沟道时,没有自由电子携带电流;此时可以说FET被夹断,发生这种情况的栅极电压称为夹断电压(pinch-off voltage (VP))。当栅极电压(Vgs)设置为或低于夹断电压时,则FET处于“关断”状态。

注意,当栅极上的电压(Vgs)为0V时,栅极肖特基结电位约为0.7V,会轻微夹断沟道,因此通过沟道的最大电流实际上可以通过在栅极上偏置少量正电压使IDSS以上增加直至达到IMAX。

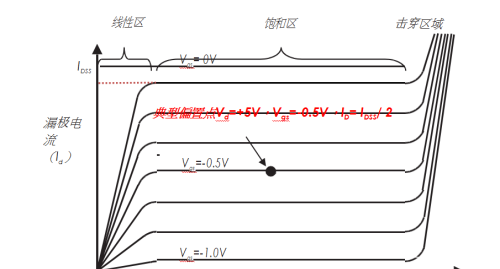

FETs的偏置沟道饱和和夹断的栅极偏置点是栅极偏置的两个极端,但FET可以偏置在两者之间的任何栅极偏置电压,最常见的偏置点是允许电流为零偏置饱和电流(IDSS/ 2)的一半的栅极电压。对于GaAs MESFET,给出IDSS/ 2的栅极偏置电压约为-0.5V。图3显示了几种不同栅极偏置电压的典型的漏极电流与漏极电压(I / V)关系图。

图3、几种不同栅极电压的FET的电流/电压(IV)曲线图

在低漏极电压时,在线性或拐点区域( knee region),漏极电流随漏极电压线性上升,直到沟道中的所有自由电子都通过电流。此时,沟道饱和,因此较高的漏极电压不会增加漏极电流。I / V图的这个区域称为饱和区域。在更高的漏极电压下,半导体材料本身发生击穿故障,电流再次迅速增加;这被称为击穿区域。

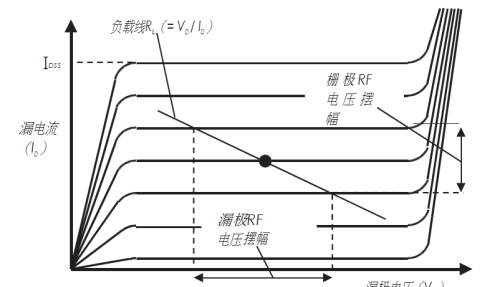

如果FET的漏极加载负载电阻RL,则改变栅极电压将导致漏极电压和电流沿着称为负载线(Load Line)的I / V曲线上的倾斜路径发生变化,如图4所示。现在可以看出,栅极端子上的小电压变化(RF信号)在漏极端子处产生更大的电压变化;换句话说,它们会产生电压增益。

图4、负载电阻RL的FET的I / V特性曲线

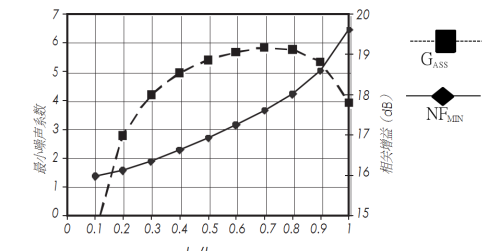

偏置点和负载电阻的不同组合用于不同的应用中;例如,功率放大器通常需要一条负载线,允许漏极电压和漏极电流的最大摆幅,以实现最大输出功率,而小信号放大器需要负载阻抗,以提供最佳的小信号增益。类似地,偏置点对于各种应用是不同的,因为FET在夹断电压附近偏置时通过的电流较小,噪声系数较低,这适用于低噪声放大器设计。然而,在夹断电压附近,电压增益也较低,因此高增益放大器通常偏置在更接近IDSS / 2。这可以在图5中看到,它显示了2x75μm pHEMT的最小噪声系数和相关增益:当漏极电流(IDS)从漏极饱和电流(IDSS)的10%变化到100%时的相应增益变化情况。

图5

图5、最小噪声系数和相关增益与IDSS漏极电流之间的关系,2x75 pHEMT工艺 [使用Agilent ADS和PH25设计套件模拟,由United Monolithic Semiconductors(UMS)提供]

线性度也是有源器件的一个重要特性,它可以测量漏极电流随负载线的栅极电压变化的线性变化。从图中可以看出,它是I / V曲线在偏置点周围的平行和均匀间隔的度量。这通常在I / V图的中间是最佳的,并且主要是器件技术的函数,GaAs MESFET和Si横向双扩散金属氧化物半导体(LDMOS)晶体管通常比Si双极晶体管更加适合在线性 放大器中应用。

MESFET金属半导体场效应晶体管(MESFET)之所以被称为这个名称是因为栅极接触是由金属 - 半导体结形成的。如果半导体材料仅是低掺杂的,则栅极金属和半导体之间产生的肖特基接触,从而使半导体工程师能够制成非常低泄漏的栅极接触。

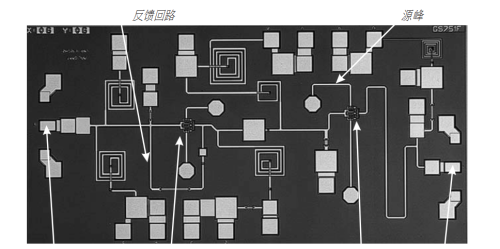

HEMT器件高电子迁移率晶体管(HEMT)与任何其他FET一样工作,除了沟道由两种不同类型的半导体材料(称为异质结)的结构成,以使通道中的自由电子具有更高的迁移率。对于GaAs HEMT,其他半导体材料通常是铝镓砷(AlGaAs)。由n型掺杂剂原子提供的自由电子非常靠近异质结,并形成所谓的二维电子气。这种二维(2D)电子气体被限制远离晶格原子,因此它们不会与它们碰撞,这使电子具有更高的迁移率。电子经历较少碰撞的另一个后果是HEMT的噪声系数远低于普通FET的噪声系数。为卫星接收器开发的HEMT LNA MMIC示例如图6所示。

图6、HEMT MMIC LNA。(由TM R&D,马来西亚提供)

HEMT在文献中有时被称为异质结构FET 或异质结FET(HFET),甚至是调制掺杂FET(MODFET),但它们都是高电子迁移率场效应晶体管(HEMTs),因为它们在不同类型的半导体之间具有异质结,这增加了载流子在沟道中的迁移率。假晶HEMT(pHEMT)使用极薄的不同半导体层[通常为铟镓砷(InGaAs)],其应变为周围半导体(通常为AlGaAs)的晶格常数,形成假晶层(具有AlGaAs晶格尺寸的InGaAs层);这样就可以获得InGaAs增强的电子传输特性,同时仍然在GaAs衬底上制造出完整的MMIC 。变质(metamorphic)HEMT(mHEMT)具有更高迁移率的半导体层,例如InP,在其表面上生长,具有其自身的自然晶格常数。为实现这一目标,GaAs衬底的晶格常数必须通过外延层逐渐改变为InP 。

温馨提示:通过以上关于MMIC电路设计中的场效应晶体管(FET)技术介绍内容介绍后,相信大家有新的了解,更希望可以对你有所帮助。