射频电路设计中阻抗匹配的必要性有哪些(射频电路设计中阻抗匹配的必要性是)

导语:射频电路设计中阻抗匹配的必要性

到目前为止,我们已经强调了阻抗匹配在射频电路设计中的重要性。 这是因为射频电路设计的主要任务是功率传输或功率控制。 为了最大限度地提高功率传输效率而又不发生相移,阻抗匹配就成为了一项不可或缺的技术。 对于大多数射频电路模块而言,输入阻抗必须与前一级电路的输出阻抗相匹配,其输出阻抗必须与下一阶段的输入阻抗相匹配。

没有人会怀疑阻抗匹配在RF或RFIC设计中的重要性。 然而,阻抗匹配又存在一些悖论。 例如,

• 是否有必要将阻抗从一部件匹配到另一个部件?

• 在阻抗匹配网络中,部件之间的阻抗一般不匹配。 是否有必要在网络本身的两个部分之间插入“子阻抗匹配网络”?

• 是否所有的射频功能模块都需要阻抗匹配?

等等。

为了回答这些问题,我们应该回到阻抗匹配的目标:它们是(一)最大限度地提高功率传输,(二)消除功率传输中的相移。 因此,功率传输单元之间需要阻抗匹配,但各个部件之间不需要阻抗匹配。

如果阻抗匹配网络由多个部分组成,则意味着网络中的所有部件都必须进行合作,以最大限度地提高功率传输效率和消除相移。 换句话说,阻抗匹配网络,而不是单独的部件,而是一个不可分割的基本实体或一个“最小单元”。它们的部件在功率传输的过程中是不可分割的。 各个部件之间的进行阻抗匹配是毫无意义的。

一般来说,必须在两个基本的功率传输单元之间进行阻抗匹配。

有两个例外情况我们没有这样做,它们分别是:

1. 这两个基本的功率传输单元结合在一起,用于特殊的性能要求。

2. 阻抗不可能匹配,也不能匹配:例如从VCO(电压控制振荡器)或振荡器的输出到下一个电路块的输入。

让我们举例来说明这一点。

图1

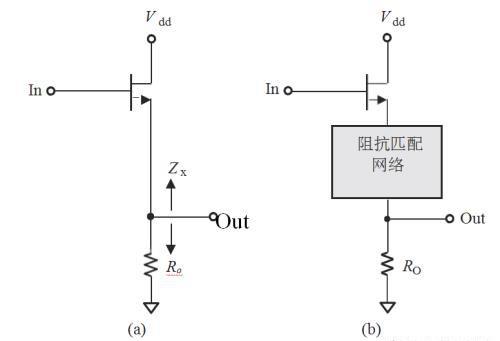

图1、 源跟随器(忽略直流偏置)(a)原始的源跟随器;(b) “改进”的源跟随器

示例1:图1(a)显示了一个源跟随器,其输出没有阻抗匹配(忽略直流偏置)。 它由MOSFET(金属氧化物半导体场效应晶体管)和输出电阻R0组成的 。 看图2(A)中晶体管的发射极,可以看出其阻抗为Zx 通常不是采用消除电阻R0那样的共轭阻抗匹配。 如果在MOSFET的源和输出电阻R0之间插入阻抗匹配网络,是否对功率传输有好处? 如图1(b)所示。

答案是:不会,因为单个MOSFET或输出电阻不是基本的或 独立的功率传输单元。 两者结合在一起构成一个基本的功率传输单元,它们之间是不可分割的..

示例2:图2显示了CS-CG级联LNA(低噪声amplifier).. 如果在CS晶体管的集电极和CG晶体管的发射极之间插入匹配网络,是否有功率传输方面的优点?

(a)

(b)

图2、 一个MOSFET级联放大器。 (a)初始的MOSFET级联放大器; (b)在两级放大器之间插入阻抗匹配网络;

在图2(A)中,第一个功率传输单元由CS晶体管和与其源和栅极连接的部件组成,第二功率传输单元由CG晶体管和与其漏极连接的部件组成的。 这些是功率传输过程中的独立单元。 如果在CS晶体管的集电极和CG晶体管的发射极之间插入阻抗匹配网络,如图3(B)所示,那么其好处是有可能能最大限度地提高功率传输效率。 然而,CS-CG级联配置将受到插入的阻抗匹配网络的严重干扰:那就是它的特殊特性,即输入米勒电容(Miller capacitance)的最小化的特征被移除或被大大地退化。 所以最好不要在CS晶体管的集电极和CG晶体管的发射极之间插入这样的阻抗匹配网络。

免责声明:本站部份内容由优秀作者和原创用户编辑投稿,本站仅提供存储服务,不拥有所有权,不承担法律责任。若涉嫌侵权/违法的,请反馈,一经查实立刻删除内容。本文内容由快快网络小璎创作整理编辑!