放大电路中去耦电容的作用(去耦电路原理)

导语:IC放大器中的“去耦”和“接地”

就像我们为系统功耗、接地及信号回路找到合适配置时,往往会引入一些干扰。在理解IC放大器的“去耦”、“接地”概念时也常常会被一些显而易见的问题所愚弄。

下面为大家阐述一个一般性原则,之后我们再慢慢讨论与集成电路放大器相关的去耦与接地问题——

首先请思考:电流流向何处?

表面来看,这是一个显而易见的问题。但提到电流时,人们一般都会想到电流从某个地方“流出”,然后“流过”其他地方,却忽视了电流如何流回源点的问题。在实际操作中,人们似乎认为所有“接地”或“电源电压”点都是相等的。但忽略了一个事实 :这些点构成电流在其中流动并产生有限电压,它们是导体网络的一部分。

如果要进行前瞻性规划,我们必须得考虑电流的起点及返回点,必须确定结果产生的电压降的作用。而这又要求对去耦及接地电路的原理有一定的了解。然而在设计采用了集成电路时,这样的信息往往无从获取与难以理解。

我们的IC放大器是非常常用的线性IC之一,但幸运的是:就功率及接地问题而言,多数运算放大器都可归入少数类别。尽管系统配置可能带来令人生畏的去耦及信号回路问题,但通过了解运算放大器,我们可以找到解决更多此类问题的基本方法。

运算放大器有四个引脚

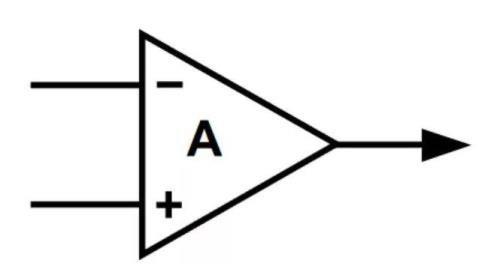

一般的读者在看过任何一本运算放大器的课本之后,可以都会认为:理想的运算放大器应该有三个引脚——一对差分输入引脚和一个输出引脚。如下图所示:

图1:常规“三端”运算放大器

但如果你真的有了解基本原理,那么必然能看出事实并非如此。如果放大器有一个输出电压,那它必然以某个点为参考进行测量。从理想运算放大器来看,它拥有无限的共模抑制性能,因而可以排除输入引脚作为参考点的可能。如此来看,必然还存在着第四个引脚。换个角度来看,如果放大器需要向负载提供输出电流,则该电流必须从某个地方进入放大器。而理想情况来看,输入电流不流动,这样一来结论仍然是“需要第四个引脚”。

一种常见的做法是在图中指出第四个引脚为“接地”端。我们不讨论什么是“接地”端,多数集成电路运算放大器(包括很多模块化运算放大器)并不存在“接地”端。对于这些电路 ,第四个引脚是电源引脚中的一个或两个。这种情况 下,人们倾向于将两个电源电压与接地归在一起。电源线路确实会在放大哭带宽范围内,在所有频率下产生较低的阻抗。然而,当阻抗要求未得到满足时,众多问题就会随之而来,包括噪声、瞬态响应差,振荡等问题。

差分至单端转换

简单运算放大器的基本要求之一是“输入端加载的全差分信号必须转换成单端输出信号”。单端指的是相对于经常被忽视的第四个引脚而言的。这可能使问题复杂化。如下图2所示:

图2:简化版“真实”运算放大器

上图所示信号流用于多种流行的集成电路系列中。虽然细节不尽相同,但基本信号路径与101、741、748、777、4136、503、515等集成电路运算放大器大致相同。电路首先将差分输入电压转换成差分电流。该输入级函数在图2中表示为PNP晶体管。然后通过与负供电轨相连的电流镜,将电流从差分转换成单端形式。电流镜像输出驱动差一个电压放大器以及作为积分器连接的功率输出级。该积分器控制着开环响应,其电容既可外加亦可内置。关于上面这种简化型号的说明大多都没有突出积分器拥有一个差分输入的事实 。由几个基极发射极电压提供正偏置,同相积分器输入则以负电源作为参考 。

显然,放大器输出与负电源之间的大部分电压差会出现在整个补偿电容中。如果负电源电压突然发生变化,积分器放大器将强制输出随之而变。当整个放大器处于闭环配置时,其输入端产生的误差信号将深度恢复输出 ,但恢复程度受限于放大哭喊的压摆率。结果就是,这类放大器可能拥有出色的低频电源抑制性能,但负电源抑制却存在较大限制。由于导致输出恢复的是流程输入端的反馈信号,因此,对于频率输出恢复的是流程输入端的反馈信号。因此,对于频率超过闭环带宽的信号,负电源抑制比将接近0。即:高速高电平电路可以通过负电源线的公共阻抗与低电平电路“通信”。

Attention:此类放大器的问题与负电源端相关。虽然正电源抑制比也可能因频率增加而下降,但其影响程度较轻。一般而言,正电源上的小瞬变只会对信号输出产出轻微影响。这些灵敏度之间的差异可能使放大器瞬态响应出现明显不对称现象。如果驱动放大器的目的是在其额定负载范围内产生正电压摆幅,则放大器将从正电源吸取电流脉冲。

这样的脉冲可能导致电源电源瞬变,但正电源抑制将最大程度地降低对放大器输出信号的。在与此相对的情况下,负输出信号将从负电源中抽取电流。如果脉冲在总线上导致“毛刺”,则欠佳的负电源抑制性能将在放大器输出端带来类似的“毛刺”。虽然正脉冲测试可以得到放大器瞬态响应,但负脉冲测试实际上可以助您更好地了解电源负轨瞬态响应,而不是放大器响应!

事实上,电源脉冲响应本身并不是放大器上可能出现的东西。30或40厘米的电线可以充当一下高Q电厂,从而给阻尼通常过高的电源响应增加高频成分。在放大器附近安装一个去耦电容也不一定能解决问题,因为电源必须在某个地方去耦。如果去耦电流注过较长路径 ,仍有可能产生不良毛刺。

图3所示为负电源去耦的三种可能配置。在3a中,虚线表示通过去耦线路及接地线路的负信号电流路径。如果负载“接地”及去耦“接地”在电源处相接,则接地线路上的毛刺类似于负电源总线上的毛刺。根据反馈及信号源的“接地”方式,去耦电容导致的有效干扰可能大于电容的设计抗干扰能力。

图3a:无效负电源去耦

图3b展示了如何利用去耦电容降低V形及接地总线的干扰。负载电流中的高频成分被限制在一个不含接地路径的环路中。如果电容的容量够大、质量符合要求,则可降低负电源上的毛刺而不干扰输入或输出信号路径 。

图3b:针对“接地”负载优化的去耦负电源

如果负载情况复杂(如图3c),则需要进行更多的思考。如放大器驱动的是流向虚拟地的负载,则实际负载电流不会返回接地。相反,该电源必然由形成虚拟地的放大器提供。

图3c:针对 “虚拟地”负载优化的去耦负电源

在这种情况下,如果将第一放大器的负电源去耦至第二放大器的正电源,则会闭合快速信号电流环路而不干扰接地路径或信号路径 。当然,为了避免干扰输出基准电压源,必须为第二放大器提供从接地至V形总线的低阻抗路径。理解去耦电路的关键在于认清实际负载和信号电流的去向。而优化电路的关键是在接地等信号路径旁路这些电流。

考虑整个电路时,通常会出现冲突。例如,多个放大器可能由同一电源驱动,而每个放大器又需要独立的去耦电容。总体而言,去耦电容全部呈并联 状态。然而,事实 上,互连电源的电厂及接地线路 会将这种看似无碍的配置转换成一个复杂的 L-C 网络。在处理快速信号波阵面的电路中,通过数厘米线缆并联的去耦网络通常意味着麻烦。

图4:并联去耦谐振阻尼

图4展示了通过小电阻来降低 不良谐振电路 Q 值的方法。一般情况下,这些电阻是可以容许的,因为它们在运算放大器电源端将不良高频叮当声转换成小阻尼信号。虽然剩余信号具有较多的低频成分,但可以通过运算放大器的电源抑制性能而予以处理。

本文内容由小森整理编辑!